# Intel<sup>®</sup> Xeon<sup>®</sup> Processor E5 v2 Product Family

**Datasheet- Volume Two: Registers**

March 2014

Reference Number: 329188-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

A "Mission Critical Application" is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL'S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS' FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com/design/literature.htm.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

No computer system can provide absolute security under all conditions. Intel® Trusted Execution Technology (Intel® TXT) requires a computer with Intel® Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). Intel TXT also requires the system to contain a TPM v1.s. For more information, visit http://www.intel.com/technology/security

Requires a system with Intel® Turbo Boost Technology. Intel Turbo Boost Technology and Intel Turbo Boost Technology 2.0 are only available on select Intel® processors. Consult your PC manufacturer. Performance varies depending on hardware, software, and system configuration. For more information, visit http://www.intel.com/go/turbo

Intel® Virtualization Technology requires a computer system with an enabled Intel® processor, BIOS, and virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit http://www.intel.com/go/virtualization

ENERGY STAR is a system-level energy specification, defined by the Environmental Protection Agency, that relies on all system components, such as processor, chipset, power supply, etc.) For more information, visit http://www.intel.com/technology/epa/index.htm

The original equipment manufacturer must provide TPM functionality, which requires a TPM-supported BIOS. TPM functionality must be initialized and may not be available in all countries.

Intel, Intel Enhanced SpeedStep Technology, and the Intel logo are trademarks of Intel Corporation in the U. S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2014, Intel Corporation. All Rights Reserved.

# Contents

| 1 | Regis      | sters Ov | verview and Configuration Process               | 19 |

|---|------------|----------|-------------------------------------------------|----|

|   | 1.1        | Platforr | m Configuration Structure                       | 19 |

|   |            | 1.1.1    | Processor IIO Devices (CPUBUSNO (0))            |    |

|   |            | 1.1.2    | Processor Uncore Devices (CPUBUSNO (1))         |    |

|   | 1.2        |          | uration Register Rules                          |    |

|   |            | 1.2.1    | CSR Access                                      |    |

|   |            | 1.2.2    | MSR Access                                      |    |

|   |            | 1.2.3    | Memory-Mapped I/O Registers                     |    |

|   | 1.3        |          | er Terminology                                  |    |

|   | 1.4        |          | ed Processor Inventory Number                   |    |

|   |            |          | -                                               |    |

| 2 | -          |          | Nemory Controller (IMC) Configuration Registers |    |

|   | 2.1        |          | Xeon® Processor E5 v2 Processor registers.      |    |

|   | 2.2        |          | Xeon® Processor E5-2400 v2 Processor registers. |    |

|   | 2.3        |          | 15 Function 0                                   |    |

|   |            | 2.3.1    | рхрсар                                          |    |

|   |            | 2.3.2    | mcmtr                                           |    |

|   |            | 2.3.3    | tadwayness_[0:11]                               |    |

|   |            | 2.3.4    | mcmtr2                                          | 34 |

|   |            | 2.3.5    | mc_init_state_g                                 | 34 |

|   |            | 2.3.6    | rcomp_timer                                     | 35 |

|   |            | 2.3.7    | mh_maincntl                                     | 36 |

|   |            | 2.3.8    | mh_sense_500ns_cfg                              | 37 |

|   |            | 2.3.9    | mh_dtycyc_min_asrt_cntr_[0:1]                   | 38 |

|   |            | 2.3.10   | mh_io_500ns_cntr                                | 39 |

|   |            | 2.3.11   | mh_chn_astn                                     | 39 |

|   |            | 2.3.12   | mh_temp_stat                                    | 40 |

|   |            | 2.3.13   | mh_ext_stat                                     | 41 |

|   |            |          | smb_stat_[0:1]                                  |    |

|   |            |          | smbcmd_[0:1]                                    |    |

|   |            |          | smbcntl_[0:1]                                   |    |

|   |            |          | smb_tsod_poll_rate_cntr_[0:1]                   |    |

|   |            |          | smb_period_cfg                                  |    |

|   |            |          | smb_period_cntr                                 |    |

|   |            |          | smb_tsod_poll_rate                              |    |

|   | 2.4        |          | 15 Function 1                                   |    |

|   |            | 2.4.1    | рхрсар                                          |    |

|   |            | 2.4.2    | spareaddresslo                                  |    |

|   |            | 2.4.3    | sparectl                                        |    |

|   |            | 2.4.4    | ssrstatus                                       |    |

|   |            | 2.4.5    | scrubaddresslo                                  |    |

|   |            | 2.4.6    | scrubaddresshi                                  |    |

|   |            | 2.4.7    | scrubctl                                        |    |

|   |            | 2.4.8    | spareinterval                                   |    |

|   |            | 2.4.0    | rasenables                                      |    |

|   |            |          |                                                 |    |

|   |            |          | smisparectl                                     |    |

|   |            | 2.4.11   |                                                 |    |

|   |            |          | leaky_bucket_cntr_lo                            |    |

|   | <u>а г</u> |          | leaky_bucket_cntr_hi                            |    |

|   | 2.5        |          | 15 Functions 2-5                                |    |

|   |            | 2.5.1    | pxpcap                                          |    |

|   |            | 2.5.2    | dimmmtr_[0:2]                                   |    |

|   |            | 2.5.3    | pxpenhcap                                       | 61 |

| 2.6  | Device   | 16 Functions 0, 1, 4, 561                      |

|------|----------|------------------------------------------------|

|      | 2.6.1    | рхрсар64                                       |

|      | 2.6.2    | chn_temp_cfg64                                 |

|      | 2.6.3    | chn_temp_stat65                                |

|      | 2.6.4    | dimm_temp_oem_[0:2]65                          |

|      | 2.6.5    | dimm_temp_th_[0:2]66                           |

|      | 2.6.6    | dimm_temp_thrt_Imt_[0:2]67                     |

|      | 2.6.7    | dimm_temp_ev_ofst_[0:2]67                      |

|      | 2.6.8    | dimmtempstat_[0:2]68                           |

|      | 2.6.9    | thrt_pwr_dimm_[0:2]69                          |

|      | 2.6.10   | tcdbp                                          |

|      | 2.6.11   | tcrap                                          |

|      | 2.6.12   | tcrwp                                          |

|      | 2.6.13   | tcothp                                         |

|      | 2.6.14   | tcrfp                                          |

|      | 2.6.15   | tcrftp                                         |

|      | 2.6.16   | tcsrftp                                        |

|      |          | tcmr2shadow                                    |

|      | 2.6.18   | tczqcal                                        |

|      | 2.6.19   | tcstagger_ref                                  |

|      | 2.6.20   | tcmr0shadow                                    |

|      | 2.6.21   | rpqage                                         |

|      |          | idletime                                       |

|      |          | rdimmtimingcntl                                |

|      |          | rdimmtimingcntl2                               |

|      | 2.6.25   | tcmrs                                          |

|      |          | mc_init_stat_c80                               |

| 2.7  |          | 16, Functions 2, 3, 6, 7                       |

|      | 2.7.1    | correrrcnt_083                                 |

|      | 2.7.2    | correrrcnt_1                                   |

|      | 2.7.3    | correrrcnt_284                                 |

|      | 2.7.4    | correrrcnt_385                                 |

|      | 2.7.5    | correrrthrshld_085                             |

|      | 2.7.6    | correrrthrshld_186                             |

|      | 2.7.7    | correrrthrshld_286                             |

|      | 2.7.8    | correrrthrshld_386                             |

|      | 2.7.9    | correrrorstatus                                |

|      |          | leaky_bkt_2nd_cntr_reg87                       |

|      |          | devtag_cntl_[0:7]                              |

|      |          | 0                                              |

| R2P0 |          |                                                |

| 3.1  | Device   | 19 Function 091                                |

| Inte | I® Quick | Area interconnect (Intel® QPI Agent) Registers |

| 4.1  |          | uickPath Interconnect Link Layers Registers    |

|      | 4.1.1    | QPIMISCSTAT: Intel QPI Misc Status             |

|      | 4.1.2    | FWDC_LCPKAMP_CFG                               |

|      |          |                                                |

| Inte |          | Path Interconnect Ring (R3QPI) Registers95     |

| 5.1  | Device   | 19 Function 495                                |

|      | 5.1.1    | VID                                            |

|      | 5.1.2    | DID                                            |

|      | 5.1.3    | PCICMD                                         |

|      | 5.1.4    | PCISTS97                                       |

|      | 5.1.5    | rid98                                          |

|      | 5.1.6    | ccr                                            |

|      | 5.1.7    | CLSR                                           |

|      | 5.1.8    | PLAT                                           |

|     | 5.1.9  | HDR                | . 99  |

|-----|--------|--------------------|-------|

|     | 5.1.10 | BIST               | . 99  |

|     |        | SVID               |       |

|     |        | SDID               |       |

|     |        | CAPPTR             |       |

|     |        |                    |       |

|     |        | INTL               |       |

|     |        | INTPIN             |       |

|     |        | MINGNT             |       |

|     | 5.1.17 | MAXLAT             | 100   |

|     | 5.1.18 | R3QQRT             | 100   |

|     | 5.1.19 | R3QRTE[0:1]CR      | 102   |

|     | 5.1.20 | R3QCBOHACR         | 102   |

|     | 5.1.21 | R3QE[0:1]CR        | 103   |

|     |        | R3QPCIR[0:1]CR     |       |

|     |        | R3QCTRL            |       |

|     | 5 1 24 | R3SNPFANOUT_P[0:1] | 10/   |

|     |        | R3QTxTRH.          |       |

|     |        |                    |       |

|     |        | R3QRRC             |       |

|     |        | R2IGRSPARECSR      |       |

|     |        | R3QIGRVNSEL0       |       |

|     |        | R3QIGRVNSEL1       |       |

|     | 5.1.30 | R3_GL_ERR_CFG      | 107   |

|     | 5.1.31 | R3BGFTUNE          | 107   |

|     | 5.1.32 | R3EGRCTRL          | 107   |

|     | 5.1.33 | R3QEGR1VNSEL       | 108   |

|     | 5.1.34 | R3QINGCTL          | 108   |

|     | 5.1.35 | R3QINGADVNACTL     | 108   |

|     | 5.1.36 | R3INGADTXQCTL      | 109   |

|     |        | R3INGVN0SMCRDCTL   |       |

|     |        | R3EGRERRLOG[0:1]   |       |

|     |        | R3EGRERRMSK[0:1]   |       |

|     |        | R3INGERRLOG0       |       |

|     |        | R3INGERRMASKO      |       |

|     |        | R3INGERRLOG1       |       |

|     |        |                    |       |

|     |        | R3INGERRMASK1      |       |

|     |        | R3UTLSPARECSR.     |       |

|     |        | R3INGERRLOG_MISC   |       |

|     |        | R3QDEBUG           |       |

| 5.2 |        | 19 Function 5 - 6  |       |

|     | 5.2.1  | VID                |       |

|     | 5.2.2  | DID                | 117   |

|     | 5.2.3  | PCICMD             | 118   |

|     | 5.2.4  | PCISTS             | 118   |

|     | 5.2.5  | rid                | 119   |

|     | 5.2.6  | ccr                | 119   |

|     | 5.2.7  | CLSR               | 119   |

|     | 5.2.8  | PLAT               | 119   |

|     | 5.2.9  | HDR                |       |

|     |        | BIST               |       |

|     |        | SVID               |       |

|     |        | SDID               |       |

|     |        | CAPPTR             |       |

|     |        |                    | . – - |

|     |        | INTL               |       |

|     |        |                    |       |

|     |        | MINGNT             |       |

|     | 5.2.17 | MAXLAT             | 121   |

|   |       | 5.2.18   | PMONCNTRLOWER0_[0:2]           | 1 | 22 |

|---|-------|----------|--------------------------------|---|----|

|   |       | 5.2.19   | PMONCNTRUPPER[0:1]_[0:2]       | 1 | 22 |

|   |       | 5.2.20   | PMONCNTRCFG[0:1]_[0:2]         | 1 | 22 |

|   |       |          | PMONUNITCTRL[0:1]              |   |    |

|   |       |          | PMONCTRSTATUS[0:1]             |   |    |

|   | 5.3   |          | 20 Function 1                  |   |    |

|   |       |          | VID                            |   |    |

|   |       | 5.3.2    | DID                            |   |    |

|   |       | 5.3.3    | PCICMD                         |   |    |

|   |       | 5.3.4    | PCISTS                         |   |    |

|   |       | 5.3.5    | rid                            |   |    |

|   |       | 5.3.6    | ССГ                            |   |    |

|   |       | 5.3.7    | CLSR                           |   |    |

|   |       | 5.3.8    | PLAT                           |   |    |

|   |       | 5.3.9    | HDR                            |   |    |

|   |       |          | BIST                           |   |    |

|   |       |          | SVID                           |   |    |

|   |       |          | SDID                           |   |    |

|   |       |          | CAPPTR                         |   |    |

|   |       |          | INTL                           |   |    |

|   |       |          | INTE                           |   |    |

|   |       |          | MINGNT                         |   |    |

|   |       |          |                                |   |    |

|   |       |          | MAXLAT                         |   |    |

|   |       |          | RC_IOTHUB_CR0<br>RC_IOTHUB_CR1 |   |    |

|   |       |          | RC_IOTHUB_CR2                  |   |    |

|   |       |          |                                |   |    |

|   |       |          | RC_IOTHUB_CR3                  |   |    |

|   |       |          | RC_IOTEGR_CR0                  |   |    |

|   |       |          | RC_IOTEGR_CR1                  |   |    |

|   |       |          | RC_IOTEGR_CR2<br>RC_IOTEGR_CR3 |   |    |

|   |       |          |                                |   |    |

| 6 | Proce | essor Ut | tility Box (UBOX) Registers    | 1 | 35 |

|   | 6.1   | Device   | 11 Function 0                  | 1 | 35 |

|   |       | 6.1.1    | CPUNODEID                      | 1 | 36 |

|   |       | 6.1.2    | IntControl                     | 1 | 36 |

|   |       | 6.1.3    | GIDNIDMAP                      | 1 | 37 |

|   |       | 6.1.4    | CoreCount                      | 1 | 38 |

|   |       | 6.1.5    | UBOXErrSts                     | 1 | 38 |

|   | 6.2   | Device   | 11 Function 2                  | 1 | 39 |

|   | 6.3   | Device   | 11 Function 3                  | 1 | 40 |

|   |       | 6.3.1    | CPUBUSNO                       | 1 | 41 |

|   |       | 6.3.2    | SMICtrl                        | 1 | 41 |

| - | David |          | oller Unit (PCU) Register      | 1 | 10 |

| 7 |       |          |                                |   |    |

|   | 7.1   |          | 10 Function 0                  |   |    |

|   |       | 7.1.1    | MEM_TRML_TEMPERATURE_REPORT    |   |    |

|   |       | 7.1.2    | MEM_ACCUMULATED_BW_CH_[0:3]    |   |    |

|   |       | 7.1.3    | PACKAGE_POWER_SKU              |   |    |

|   |       | 7.1.4    | PACKAGE_POWER_SKU_UNIT         |   |    |

|   |       | 7.1.5    | PACKAGE_ENERGY_STATUS          |   |    |

|   |       | 7.1.6    | Package_Temperature            |   |    |

|   |       | 7.1.7    | P_State_Limits                 |   |    |

|   |       | 7.1.8    | TEMPERATURE_TARGET             |   |    |

|   |       | 7.1.9    | SSKPD                          |   |    |

|   |       |          | C2C3TT<br>CSR_DESIRED_CORES    |   |    |

|   |       | 1 1 1 1  |                                | 1 | 40 |

|   |       | 7.1.12  | PACKAGE_RAPL_PERF_STATUS                                      | 150 |

|---|-------|---------|---------------------------------------------------------------|-----|

|   |       | 7.1.13  | DRAM_POWER_INFO                                               | 151 |

|   |       | 7.1.14  | DRAM_ENERGY_STATUS                                            | 151 |

|   |       | 7.1.15  | DRAM_ENERGY_STATUS_CH[0:3]                                    | 152 |

|   |       | 7.1.16  | DRAM_RAPL_PERF_STATUS                                         | 152 |

|   |       | 7.1.17  | MCA_ERR_SRC_LOG                                               | 153 |

|   |       | 7.1.18  | THERMTRIP_CONFIG                                              | 153 |

|   |       | 7.1.19  | CAP_HDR                                                       | 155 |

|   |       | 7.1.20  | CAPIDO                                                        | 155 |

|   |       | 7.1.21  | CAPID1                                                        | 158 |

|   |       |         | CAPID2                                                        |     |

|   |       |         | CAPID3                                                        |     |

|   |       |         | CAPID4                                                        |     |

|   |       | 7.1.25  | RESOLVED_CORES_MASK                                           | 164 |

| 8 | Intec | rated I | /O (IIO) Configuration Registers                              | 165 |

|   | 8.1   |         | rs Overview                                                   |     |

|   |       | 8.1.1   | Configuration Registers (CSR)                                 |     |

|   |       | 8.1.2   | BDF:BAR# for Various MMIO BARs in IIO                         |     |

|   |       | 8.1.3   | Unimplemented Devices/Functions and Registers                 |     |

|   |       | 8.1.4   | PCI Vs. PCIe Device / Function                                |     |

|   | 8.2   | Device  | 0 Function 0 DMI, Device 0 Function 0 PCIe, Device 1          |     |

|   |       |         | n 0-1, Device 2 Function 0-3 PCIe, Device 3 Function 0-3 PCIe | 166 |

|   |       | 8.2.1   | vid                                                           |     |

|   |       | 8.2.2   | did                                                           | 171 |

|   |       | 8.2.3   | pcicmd                                                        | 172 |

|   |       | 8.2.4   | pcists                                                        | 173 |

|   |       | 8.2.5   | rid                                                           | 175 |

|   |       | 8.2.6   | ссг                                                           | 176 |

|   |       | 8.2.7   | clsr                                                          | 176 |

|   |       | 8.2.8   | plat                                                          | 176 |

|   |       | 8.2.9   | hdr                                                           | 177 |

|   |       | 8.2.10  | bist                                                          | 177 |

|   |       | 8.2.11  | pbus                                                          | 178 |

|   |       | 8.2.12  | secbus                                                        | 178 |

|   |       | 8.2.13  | subbus                                                        | 178 |

|   |       | 8.2.14  | iobas                                                         | 179 |

|   |       | 8.2.15  | iolim                                                         | 179 |

|   |       | 8.2.16  | secsts                                                        | 180 |

|   |       | 8.2.17  | mbas                                                          | 181 |

|   |       |         | mlim                                                          |     |

|   |       | 8.2.19  | pbas                                                          | 182 |

|   |       | 8.2.20  | plim                                                          | 183 |

|   |       | 8.2.21  | pbasu                                                         | 183 |

|   |       | 8.2.22  | plimu                                                         | 184 |

|   |       |         | capptr                                                        |     |

|   |       |         | intl                                                          |     |

|   |       |         | intpin                                                        |     |

|   |       |         | bctrl                                                         |     |

|   |       |         | scapid                                                        |     |

|   |       |         | snxtptr                                                       |     |

|   |       |         | svid                                                          |     |

|   |       |         | sdid                                                          |     |

|   |       |         | dmircbar                                                      |     |

|   |       |         | msicapid                                                      |     |

|   |       |         | msinxtptr                                                     |     |

|   |       | 8.2.34  | msimsgctl                                                     | 189 |

|        | msgadr            |     |

|--------|-------------------|-----|

|        | msgdat            |     |

| 8.2.37 | msimsk            | 191 |

|        | msipending        |     |

| 8.2.39 | pxpcapid          | 191 |

|        | pxpnxtptr         |     |

|        | рхрсар            |     |

|        | devcap            |     |

|        | devctrl           |     |

|        | devsts            |     |

|        | Inkcap            |     |

|        | Inkcon            |     |

|        | Inksts            |     |

|        | sltcap            |     |

|        | sitcon            |     |

|        | sitsts            |     |

|        | rootcon           |     |

|        | rootcap           |     |

|        | rootsts           |     |

|        |                   |     |

|        | devcap2           |     |

|        | devctrl2          |     |

|        | Inkcap2           |     |

|        | Inkcon2           |     |

|        | Inksts2           |     |

|        | pmcap             |     |

|        | pmcsr             |     |

|        | xpreut_hdr_ext    |     |

|        | xpreut_hdr_cap    |     |

|        | xpreut_hdr_lef    |     |

|        | acscaphdr         |     |

|        | acscap            |     |

|        | acsctrl           |     |

|        | apicbase          |     |

|        | apiclimit         |     |

|        | vsecphdr          |     |

|        | vshdr             |     |

| 8.2.71 | errcaphdr         | 223 |

| 8.2.72 | uncerrsts         | 223 |

| 8.2.73 | uncerrmsk         | 224 |

| 8.2.74 | uncerrsev         | 224 |

| 8.2.75 | corerrsts         | 225 |

| 8.2.76 | corerrmsk         | 225 |

| 8.2.77 | errcap            | 226 |

|        | hdrlog[0:3]       |     |

|        | rperrcmd          |     |

|        | rperrsts          |     |

|        | errsid            |     |

|        | perfctrlsts_0     |     |

|        | perfetrists_0     |     |

|        | miscctrlsts_0     |     |

|        | miscetrists_0     |     |

|        | pcie_iou_bif_ctrl |     |

|        | dmictrl           |     |

|        | dmictri           |     |

|        | ERRINJCAP         |     |

|        |                   |     |

| 8.2.90 | ERRINJHDR         | 231 |

|     | 8.2.91  | ERRINJCON                    | 238 |

|-----|---------|------------------------------|-----|

|     | 8.2.92  | ctoctrl                      | 239 |

|     | 8.2.93  | xpcorerrsts                  | 239 |

|     | 8.2.94  | xpcorerrmsk                  | 239 |

|     | 8.2.95  | xpuncerrsts                  | 240 |

|     | 8.2.96  | xpuncerrmsk                  | 240 |

|     | 8.2.97  | xpuncerrsev                  | 241 |

|     | 8.2.98  | xpuncerrptr                  | 242 |

|     | 8.2.99  | uncedmask                    | 242 |

|     | 8.2.100 | Deoredmask                   | 243 |

|     | 8.2.101 | Irpedmask                    | 243 |

|     | 8.2.102 | xpuncedmask                  | 243 |

|     | 8.2.103 | Sxpcoredmask                 | 244 |

|     |         | xpglberrsts                  |     |

|     |         | 5xpglberrptr                 |     |

|     |         | pxp2cap                      |     |

|     |         | /Inkcon3                     |     |

|     |         | Binerrsts                    |     |

|     |         | 9In[0:3]eq                   |     |

|     |         | )In[4:7]eq                   |     |

|     |         | l ln [8: 15]eq               |     |

|     |         | ۱er_cap                      |     |

|     |         | Bler_hdr                     |     |

|     |         | <br>Her_ctrlsts              |     |

|     |         | jler_uncerrmsk               |     |

|     |         | <br>bler_xpuncerrmsk         |     |

|     |         | 70-1ler_rperrmsk             |     |

|     |         | 3xppmdl[0:1]                 |     |

|     |         | Pxppmcl[0:1]                 |     |

|     |         | )xppmdh                      |     |

|     |         | xppmch                       |     |

|     |         | 2xppmr[0:1]                  |     |

|     |         | 3xppmevl[0:1]                |     |

|     |         | kxppmevh[0:1]                |     |

|     |         | 5xppmer[0:1]                 |     |

| 8.3 |         | 0 Function 0 Region DMIRCBAR |     |

| 0.5 | 8.3.1   | dmivcOrcap                   |     |

|     | 8.3.2   | dmivcOrctl                   |     |

|     | 8.3.3   | dmivc0rsts                   |     |

|     | 8.3.4   | dmivc1rcap                   |     |

|     | 8.3.5   | dmiverreap<br>dmivc1rctl     |     |

|     | 8.3.6   | dmive1ret                    |     |

|     | 8.3.7   | dmivcprcap                   |     |

|     | 8.3.8   | dmivcprctl                   |     |

|     | 8.3.9   | dmivcprsts                   |     |

|     | 8.3.10  | •                            |     |

|     | 8.3.10  | •                            |     |

|     |         | dmivimrsts                   |     |

|     |         | dmivc1cdtthrottle            |     |

|     |         |                              |     |

|     |         | dmivcpcdtthrottle            |     |

| 0 / |         | dmivcmcdtthrottle            |     |

| 8.4 | 8.4.1   |                              |     |

|     |         | vid                          |     |

|     | 8.4.2   | did                          |     |

|     | 8.4.3   | pcicmd                       |     |

|     | 8.4.4   | pcists                       | 211 |

|     | 8.4.5  | rid                                  | . 278 |

|-----|--------|--------------------------------------|-------|

|     | 8.4.6  | CCr                                  | . 278 |

|     | 8.4.7  | clsr                                 | . 279 |

|     | 8.4.8  | hdr                                  | . 279 |

|     | 8.4.9  | cb_bar                               | . 279 |

|     | 8.4.10 | svid                                 | . 280 |

|     |        | sdid                                 |       |

|     |        | capptr                               |       |

|     |        | intl                                 |       |

|     |        | intpin                               |       |

|     |        | devcfg                               |       |

|     |        | msixcapid                            |       |

|     |        | msixnxtptr                           |       |

|     |        | msixmsgctl                           |       |

|     |        | tableoff_bir                         |       |

|     |        | pbaoff_bir                           |       |

|     |        | capid                                |       |

|     |        | nextptr                              |       |

|     |        | ехрсар                               |       |

|     |        | devcap                               |       |

|     |        | devcon                               |       |

|     |        | devsts                               |       |

|     |        | devcap2                              |       |

|     |        | devcon2                              |       |

|     |        | pmcap                                |       |

|     |        | pmcsr                                |       |

|     |        | dmauncerrsts                         |       |

|     |        | dmauncerrmsk                         |       |

|     |        | dmauncerrsev                         |       |

|     |        | dmauncerrptr                         |       |

|     |        | dmaglberrptr                         |       |

|     |        | chanerr_int                          |       |

|     |        | chanerrmsk_int                       |       |

|     |        | chanerrsev_int                       |       |

|     |        | chanerrptr                           |       |

| 8.5 |        | 4 Function 0 - 7 MMIO Region CB_BARs |       |

|     | 8.5.1  | chancnt                              |       |

|     | 8.5.2  | xfercap                              |       |

|     | 8.5.3  | genctrl                              | . 298 |

|     | 8.5.4  | intrctrl                             |       |

|     | 8.5.5  | attnstatus                           | . 299 |

|     | 8.5.6  | cbver                                |       |

|     | 8.5.7  | intrdelay                            | . 300 |

|     | 8.5.8  | cs_status                            | . 300 |

|     | 8.5.9  | dmacapability                        | . 300 |

|     | 8.5.10 | dcaoffset                            | . 302 |

|     | 8.5.11 | cbprio                               | . 302 |

|     | 8.5.12 | chanctrl                             | . 303 |

|     | 8.5.13 | dma_comp                             | . 304 |

|     | 8.5.14 | chancmd                              | . 305 |

|     | 8.5.15 | dmacount                             | . 305 |

|     | 8.5.16 | chansts_0                            | . 305 |

|     | 8.5.17 | chansts_1                            | . 306 |

|     | 8.5.18 | chainaddr_0                          | . 306 |

|     | 8.5.19 | chainaddr_1                          | . 307 |

|     | 8.5.20 | chancmp_0                            | . 307 |

|     | 8.5.21 | chancmp_1               | 307 |

|-----|--------|-------------------------|-----|

|     | 8.5.22 | chanerr                 | 308 |

|     | 8.5.23 | chanerrmsk              | 310 |

|     | 8.5.24 | dcactrl                 | 310 |

|     | 8.5.25 | dca_ver                 | 311 |

|     | 8.5.26 | dca_regid_offset        | 311 |

|     | 8.5.27 | csi_capability          | 311 |

|     |        | pcie_capability         |     |

|     |        | csi_cap_enable          |     |

|     |        | pcie_cap_enable         |     |

|     |        | apicid_tag_map          |     |

|     |        | dca_reqid[0:1]          |     |

|     |        | msgaddr                 |     |

|     |        | msgupaddr               |     |

|     |        | msgdata                 |     |

|     |        | vecctrl                 |     |

|     |        | pendingbits             |     |

| 8.6 |        | 5 Function 0            |     |

| 0.0 | 8.6.1  |                         |     |

|     | 8.6.2  | did                     |     |

|     | 8.6.3  | pcicmd                  |     |

|     | 8.6.4  | pcists                  |     |

|     | 8.6.5  | rid                     |     |

|     | 8.6.6  | ссг                     |     |

|     | 8.6.7  | clsr                    |     |

|     | 8.6.8  | hdr                     |     |

|     | 8.6.9  | svid                    |     |

|     | 8.6.10 |                         |     |

|     | 8.6.11 |                         |     |

|     |        | intl                    |     |

|     |        | intpin                  |     |

|     |        | pxpcapid                |     |

|     |        | pxpnxtptr               |     |

|     |        | рхрсар                  |     |

|     |        | hdrtypectrl             |     |

|     |        | mmcfg_base              |     |

|     |        | mmcfg_limit             |     |

|     |        | tseg                    |     |

|     |        | genprotrange[1:0]_base  |     |

|     |        | genprotrange[1:0]_limit |     |

|     |        | genprotrange2_base      |     |

|     |        | genprotrange2_limit     |     |

|     |        | tolm                    |     |

|     | 8.6.26 | tohm                    | 327 |

|     |        | ncmem_base              |     |

|     |        | ncmem_limit             |     |

|     |        | mencmem_base            |     |

|     |        | mencmem_limit           |     |

|     |        | cpubusno                |     |

|     |        | Immiol base             |     |

|     |        | Immiol_limit            |     |

|     |        | Immioh_base             |     |

|     |        | Immioh_limit            |     |

|     |        | cipctrl                 |     |

|     |        | cipsts                  |     |

|     |        | cipdcasad               |     |

|     |        |                         |     |

|     |        | cipintrc                                 |     |

|-----|--------|------------------------------------------|-----|

|     |        | cipintrs                                 |     |

|     |        | vtbar                                    |     |

|     | 8.6.42 | vtgenctrl                                | 337 |

|     | 8.6.43 | vtgenctrl2                               | 337 |

|     | 8.6.44 | iotlbpartition                           | 339 |

|     |        | vtuncerrsts                              |     |

|     | 8.6.46 | vtuncerrmsk                              | 340 |

|     |        | vtuncerrsev                              |     |

|     |        | vtuncerrptr                              |     |

|     | 8.6.49 | iiomiscctrl                              | 342 |

|     |        | Itdpr                                    |     |

|     |        | lcfgbus_base                             |     |

|     |        | lcfgbus_limit                            |     |

|     |        | csipintrs                                |     |

| 8.7 |        | 5 Function 0 MMIO Region VTBAR           |     |

| 0.7 | 8.7.1  | vtd[0:1]_version                         |     |

|     | 8.7.2  | vtd[0:1]_cap                             |     |

|     | 8.7.3  | vtd[0:1]_ext_cap                         |     |

|     | 8.7.4  | vtd[0:1]_glbcmd                          |     |

|     | 8.7.5  | vtd[0:1]_glbsts                          |     |

|     | 8.7.6  | vtd[0:1]_gibsts<br>vtd[0:1]_rootentryadd |     |

|     | 8.7.7  | vtd[0:1]_ctxcmd                          |     |

|     | 8.7.8  | vtd[0:1]_tltsts                          |     |

|     | 8.7.9  | nonisoch_fltevtctrl                      |     |

|     |        | nonisoch_fitevtdata                      |     |

|     |        | vtd[0:1]_fltevtaddr                      |     |

|     |        | vtd[0:1]_fitevtupraddr                   |     |

|     |        | vtd[0:1]_pmen                            |     |

|     |        | vtd[0:1]_prot_low_mem_base               |     |

|     |        | vtd[0:1]_prot_low_mem_limit              |     |

|     |        | vtd[0:1]_prot_high_mem_base              |     |

|     |        | vtd[0:1]_prot_high_mem_limit             |     |

|     |        | vtd[0:1]_inv_queue_head                  |     |

|     |        | vtd[0:1]_inv_queue_tail                  |     |

|     |        | vtd[0:1]_inv_queue_add                   |     |

|     |        | vtd[0:1]_inv_comp_status                 |     |

|     |        | nonisoch_inv_cmp_evtctrl                 |     |

|     |        | nonisoch_invevtdata                      |     |

|     |        | vtd[0:1]_inv_comp_evt_addr               |     |

|     |        | vtd[0:1]_inv_comp_evt_upraddr            |     |

|     |        | vtd[0:1]_intr_remap_table_base           |     |

|     |        | vtd0_fltrec[0:7]_gpa, vtd1_fltrec0_gpa   |     |

|     |        | vtd0_fltrec[0:7]_src, vtd1_fltrec0_src   |     |

|     |        | vtd[0:1]_invaddrreg                      |     |

|     |        | vtd[0:1]_invadureg                       |     |

|     |        | vid                                      |     |

|     |        | did                                      |     |

|     |        | pcicmd                                   |     |

|     |        | pcists                                   |     |

|     |        | rid                                      |     |

|     |        | CCF                                      |     |

|     |        | cci                                      |     |

|     |        | plat                                     |     |

|     |        | hdr                                      |     |

|     |        | bist                                     |     |

|     | 0.7.40 | MI3(                                     | 570 |

|     | 8.7.41 | svid             | 370 |

|-----|--------|------------------|-----|

|     |        | sdid             |     |

|     | 8.7.43 | capptr           | 371 |

|     | 8.7.44 | intl             |     |

|     | 8.7.45 | 1                |     |

|     |        | mingnt           |     |

|     |        | maxlat           |     |

|     |        | рхрсар           |     |

|     |        | msicap           |     |

|     | 8.7.50 |                  |     |

|     |        | msiar            |     |

|     |        | msidr            |     |

|     |        | memhpctrl        |     |

|     |        | xpprivc1         |     |

|     |        | memhpcap[0:3]    |     |

|     |        | memhphdr[0:3]    |     |

|     |        | sltcap[0:3]      |     |

|     |        | sltcon[0:3]      |     |

| 0.0 |        | sltsts[0:3]      |     |

| 8.8 |        | 5 Function 2     |     |

|     | 8.8.1  | vid              |     |

|     | 8.8.2  | did              |     |

|     | 8.8.3  | pcicmd           |     |

|     | 8.8.4  | pcists           |     |

|     | 8.8.5  | rid              |     |

|     | 8.8.6  | CCC              |     |

|     | 8.8.7  | clsr             |     |

|     | 8.8.8  | hdr              |     |

|     | 8.8.9  | svid             |     |

|     | 8.8.10 |                  |     |

|     |        | capptr           |     |

|     | 8.8.13 | intlintpin       |     |

|     | 8.8.14 | •                |     |

|     | 8.8.14 |                  |     |

|     |        | рхрар            |     |

|     |        | csr_sat_mask_set |     |

|     |        | cqctrl3          |     |

|     |        | cqctrl6          |     |

|     |        | cgctrl7          |     |

|     |        | cgsts            |     |

|     |        | cgstagger        |     |

|     |        | cqctrl5          |     |

|     |        | cgctrl4_0        |     |

|     |        | cgctrl4_1        |     |

|     |        | irpperrsv        |     |

|     |        | iioerrsv         |     |

|     |        | mierrsv          |     |

|     |        | pcierrsv         |     |

|     |        | sysmap           |     |

|     |        | viral            |     |

|     | 8.8.32 | errpinctl        | 393 |

|     |        | errpinsts        |     |

|     |        | errpindat        |     |

|     | 8.8.35 | vppctl           | 394 |

|     | 8.8.36 | vppsts           | 395 |

|     |        |                  |     |

|     | 8.8.37 | vppfreq                            | 6 |

|-----|--------|------------------------------------|---|

|     | 8.8.38 | vppmem                             | 6 |

|     | 8.8.39 | vpp_inverts                        | 7 |

|     | 8.8.40 | miscprivc                          | 7 |

|     | 8.8.41 | gcerrst                            | 7 |

|     |        | gcferrst                           |   |

|     |        | gcnerrst                           |   |

|     | 8.8.44 | gnerrst                            | 9 |

|     |        | gferrst                            |   |

|     | 8.8.46 | gerrctl                            | 2 |

|     | 8.8.47 | gsysst                             | 3 |

|     |        | gsysctl                            |   |

|     |        | gtime_lsb                          |   |

|     | 8.8.50 | gtime_msb                          | 4 |

|     |        | gfferrst, gfnerrst                 |   |

|     |        | gnferrst, gnnerrst                 |   |

|     |        | irpp[0:1]errst                     |   |

|     |        | irpp[0:1]errctl                    |   |

|     | 8.8.55 | irpp[0:1]fferrst, irpp[0:1]fnerrst | 6 |

|     |        | irpp[0:1]fferrhd[0:3]              |   |

|     |        | irpp[0:1]nferrst, irpp[0:1]nnerrst |   |

|     |        | irpp[0:1]nferrhd[0:3]              |   |

|     |        | irpp[0:1]errcnt                    |   |

|     |        | iioerrst                           |   |

|     |        | iioerrctl                          |   |

|     |        | iiofferrst, iiofnerrst             |   |

|     |        | iiofferrhd_[0:3]                   |   |

|     |        | iionferrst, iionnerrst             |   |

|     |        | iionferrhd_[0:3]                   |   |

|     |        | iioerrcntsel                       |   |

|     |        | iioerrcnt                          |   |

|     |        | mierrst                            |   |

|     |        | mierrctl                           |   |

|     |        | mifferrst, mifnerrst               |   |

|     |        | mifferrhdr_[0:3]                   |   |

|     |        | minferrst, minnerrst               |   |

|     |        | minferrhdr_[0:3]                   |   |

|     |        | mierrcntsel                        |   |

|     |        | mierrcnt                           |   |

| 8.9 |        | 5 Function 4                       |   |

| 0.7 |        | vid                                |   |

|     | 8.9.2  | did                                |   |

|     | 8.9.3  | pcicmd                             |   |

|     | 8.9.4  | pcists                             |   |

|     | 8.9.5  | rid                                |   |

|     | 8.9.6  | ccr                                |   |

|     | 8.9.7  | clsr                               |   |

|     | 8.9.8  | hdr                                |   |

|     | 8.9.9  | mbar                               |   |

|     |        | svid                               |   |

|     |        | svid                               |   |

|     |        | capptr                             |   |

|     |        | intlin                             |   |

|     |        | intoin                             |   |

|     |        | abar                               |   |

|     |        | pxpcap                             |   |

|     | 0.2.10 | рлроар                             |   |

|                  | 8.9.17 snapshot_index                                                                    | 422 |

|------------------|------------------------------------------------------------------------------------------|-----|

|                  | 8.9.18 snapshot_window                                                                   | 422 |

|                  | 8.9.19 ioapictetpc                                                                       |     |

|                  | 8.9.20 pmcap                                                                             |     |

|                  | 8.9.21 pmcsr                                                                             |     |

|                  | 8.9.22 ioadsels0                                                                         |     |

|                  | 8.9.23 ioadsels1                                                                         |     |

|                  | 8.9.24 iointsrc0                                                                         |     |

|                  | 8.9.25 iointsrc1                                                                         |     |

|                  | 8.9.26 ioremintcnt                                                                       |     |

|                  | 8.9.27 ioremgpecnt                                                                       |     |

| 8.10             |                                                                                          |     |

| 0.10             | 8.10.1 index                                                                             |     |

|                  | 8.10.2 window                                                                            |     |

|                  | 8.10.3 eoi                                                                               |     |

|                  | 8.10.4 Device 5 Function 4 Window 0                                                      |     |

| 8.1 <sup>-</sup> |                                                                                          |     |

| 0.1              | 8.11.1 rx_ctle_peak_gen2                                                                 |     |

|                  | 8.11.2 rx_ctle_peak_gen2                                                                 |     |

|                  | 8.11.3 rx_ctle_peak_gen3                                                                 |     |

|                  | 8.11.4 rx_ctle_peak_gen2                                                                 |     |

|                  | 8.11.5 rx_ctle_peak_gen3                                                                 |     |

| 8.12             |                                                                                          |     |

|                  | 8.12.1 Configuration Register Map (NTB Primary Side)                                     |     |

|                  | 8.12.2 Standard PCI Configuration Space - Type 0 Common Configuration Space              |     |

|                  | 8.12.3 NTB Port 3A Configured as Primary Endpoint Device                                 |     |

|                  | 8.12.4 PCI Express Configuration Registers (NTB Secondary Side)                          |     |

|                  | 8.12.5 Configuration Register Map (NTB Secondary Side)                                   |     |

|                  | 8.12.6 NTB Shadowed MMIO Space                                                           | 507 |

|                  | 8.12.7 NTB Primary/Secondary Host MMIO Registers                                         | 509 |

|                  | 8.12.8 MSI-X MMIO Registers (NTB Primary side)                                           |     |

|                  | 8.12.9 MSI-X MMIO registers (NTB Secondary Side)                                         | 528 |

| 8.13             | 5                                                                                        |     |

|                  | 8.13.1 Crystal Beach DMA Registers Maps                                                  | 530 |

| Figure           |                                                                                          |     |

| _                |                                                                                          | 10  |

| 1-1              | Processor Integrated I/O Device Map                                                      |     |

| 1-2              | Processor Uncore Devices Map                                                             | 21  |

| Tables           | 5                                                                                        |     |

| 1-1              | Functions Specifically Handled by the Processor                                          | 23  |

| 1-2              | Register Attributes Definitions                                                          |     |

| 8-1              | BDF:BAR# for Various MMIO BARs in IIO                                                    |     |

| 8-1              | Function Number of Active Root Ports in Port 1(Dev#1) based on Port Bifurcation          |     |

|                  |                                                                                          |     |

| 8-3              | Function Number of Active Root Ports in Port 2(Dev#2) based on Port Bifurcation          |     |

| 8-4              | Function Number of Active Root Ports in Port 3(Dev#3) based on Port Bifurcation          | 166 |

| 8-5              | Device 3 Function 0 (Non-Transparent Bridge) Configuration Map Offset 0x00h -<br>0xFCh   | 435 |

| 8-6              | Device 3 Function 0 (Non-Transparent Bridge) Configuration Map Offset 0x100h -<br>0x1FCh | 436 |

| 8-7              | Device 3 Function 0 (Non-Transparent Bridge) Configuration Map Offset 0x200h -           |     |

|                  | 0x2FCh                                                                                   |     |

| 8-8              | Device 0 Function 0 (Non -Transparent Bridge) Configuration Map 0x00h - 0xFCh            |     |

| 8-9              | Device 0 Function 0 (Non -Transparent Bridge) Configuration Map 0x100h - 0x1FCh          | 479 |

| 8-10 | NTB MMIO Shadow Registers                                          |     |

|------|--------------------------------------------------------------------|-----|

| 8-11 | NTB ММІО Мар                                                       |     |

| 8-12 | NTB ММІО Мар                                                       |     |

| 8-13 | MSI-X Vector Handling and Processing by IIO on Primary Side        |     |

| 8-14 | NTB ММІО Мар                                                       |     |

| 8-15 | MSI-X Vector Handling and Processing by IIO on Secondary Side      |     |

| 8-16 | Crystal Beach DMA Configuration Map. Device 4 Function 0 -7        |     |

|      | Offset 0x00H to 0x0FCH                                             |     |

| 8-17 | Crystal Beach DMA Configuration Map. Device 4 Function 0 -7 Offset |     |

|      | 0x100-0x1FF                                                        | 532 |

# **Revision History**

| Revision<br>Number | Description                                                          | Date        |  |  |  |

|--------------------|----------------------------------------------------------------------|-------------|--|--|--|

| 001                | Initial release of the document.                                     | August 2013 |  |  |  |

| 002                | Added register information for E5-2400 v2     Janua                  |             |  |  |  |

| 003                | Added Protected Processor Inventory Number Information     March 201 |             |  |  |  |

§

# 1 Registers Overview and Configuration Process

The Intel® Xeon® Processor E5 v2 product family contains one or more PCI devices within each individual functional block. The configuration registers for these devices are mapped as devices residing on the PCI Bus assigned for the processor socket.

# 1.1 Platform Configuration Structure

The DMI2 physically connects the processor and the PCH. From a configuration standpoint the DMI2 is a logical extension of PCI Bus 0. DMI2 and the internal devices in the processor IIO and PCH logically constitute PCI Bus 0 to configuration software. As a result, all devices internal to the processor and the PCH appear to be on PCI Bus 0.

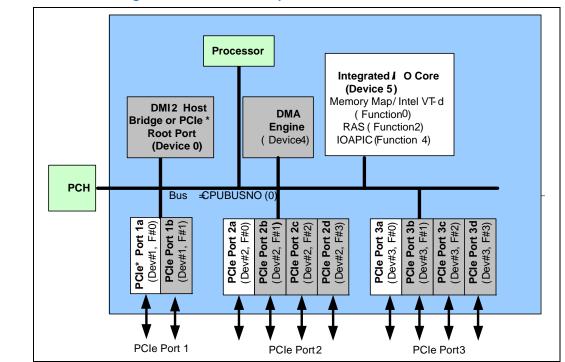

## 1.1.1 Processor IIO Devices (CPUBUSNO (0))

The processor IIO contains PCI devices within a single, physical component. The configuration registers for the devices are mapped as devices residing on PCI Bus "CPUBUSNO(0)" where CPUBUSNO(0) is programmable by BIOS.

#### Figure 1-1. Processor Integrated I/O Device Map

• **Device 0:** DMI2 Root Port. Logically this appears as a PCI device residing on PCI Bus 0. Device 0 contains the standard PCI header registers, extended PCI configuration registers and DMI2 device specific configuration registers.

- **Device 1:**PCI Express\* Root Port 1a, 1b. Logically this appears as a "virtual" PCIto-PCI bridge residing on PCI Bus 0 and is compliant with *PCI Express Local Bus Specification Revision 2.0.* Device 1 contains the standard PCI Express/PCI configuration registers including PCI Express Memory Address Mapping registers. It also contains the extended PCI Express configuration space that include PCI Express error status/control registers and Virtual Channel controls.

- **Device 2:** PCI Express\* Root Port 2a, 2b, 2c and 2d. Logically this appears as a "virtual" PCI-to-PCI bridge residing on PCI Bus 0 and is compliant with *PCI Express Local Bus Specification Revision 2.0.* Device 2 contains the standard PCI Express/ PCI configuration registers including PCI Express Memory Address Mapping registers. It also contains the extended PCI Express configuration space that include PCI Express Link status/control registers and Virtual Channel controls.

- **Device 3:** PCI Express Root Port 3a, 3b, 3c and 3d. Logically this appears as a "virtual" PCI-to-PCI bridge residing on PCI Bus 0 and is compliant with *PCI Express Local Bus Specification Revision 2.0.* Device 3 contains the standard PCI Express/ PCI configuration registers including PCI Express Memory Address Mapping registers. It also contains the extended PCI Express configuration space that include PCI Express error status/control registers and Virtual Channel controls.

- **Device 4:** Crystal Beach DMA. This device contains the Standard PCI registers for each of its functions. This device implements 8 functions for the 8 DMA Channels and also contains Memory Map I/O registers.

- Device 5: Integrated I/O Core. This device contains the Standard PCI registers for each of its functions. This device implements three functions; Function 0 contains Address Mapping, Intel<sup>®</sup> Virtualization Technology (Intel<sup>®</sup> VT) for Directed I/O (Intel<sup>®</sup> VT-d) related registers and other system management registers. Function 1 contains PCIe\* and Memory Hot-Plug registers. Function 2 contains I/O RAS registers, Function 4 contains System Control/Status registers and miscellaneous control/status registers on power management and throttling.

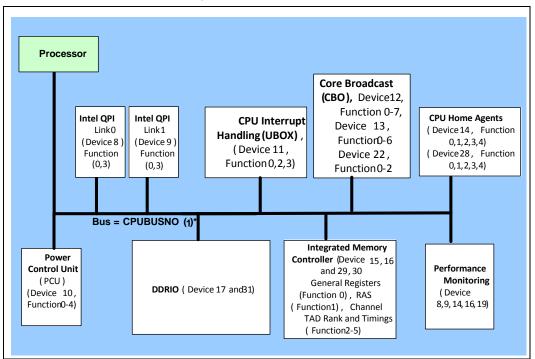

## 1.1.2 Processor Uncore Devices (CPUBUSNO (1))

The configuration registers for these devices are mapped as devices residing on the PCI bus assigned for the processor socket. Bus number is derived by the max bus range setting and processor socket number.

Figure 1-2. Processor Uncore Devices Map

- Device 8: Intel® QuickPath Interconnect (Intel® QPI) Link 0. Device 8, Function 0 and 3 contain the configurable Intel QPI Link 0 registers

- **Device 9:** Intel QPI Link 1. Device 9, Function 0 and 3 contain the configurable Intel QPI Link 1 registers.

- **Device 10:** Processor Power Control Unit. Device 10, Function 0-4 contains the configurable PCU registers.

- **Device 11:** Processor Interrupt Event Handling (UBox). Device 11, Function 0 contains the processor Interrupt control registers. Device 11, Function 3 contains the Semaphore and Scratchpad configuration registers.

- **Device 12:** Processor Core Broadcast. Device 12, Function 0-7 contains the Unicast configuration registers.

- **Device 13:** Processor Core Broadcast. Device 13, Function 0-6 contains the Unicast configuration registers

- **Device 14:** Processor Home Agent 0. Device 14, Function 0 contains the processor Home Agent Target Address configuration registers for the Memory Controller. Device 14, Function 1 contains processor Home Agent performance monitoring registers.

- **Device 15:** Integrated Memory Controller 0. Device 15, Function 0 contains the general and MemHot registers for the Integrated Memory Controller 0 and resides. Function 1 contains the RAS registers for Integrated Memory Controller 0. Device 15, Function 2-5 contains the Target Address Decode, Channels Rank and Memory Timing Registers.

- **Device 16:** DDR Channel 0,1,2,3. Device 16, Function 0, 1, 4 and 5 contains the Thermal control registers for DDR Channel 0,1,2,3. Device 16, Function 2, 3,6 and 7 contains the test registers for DDR Channel 0,1,2,3.

- **Device 18:** Processor Performance Monitoring and Ring. Device 18, Function 4 -6 contains the processor Ring to Intel QPI Link 2, Intel QPI agent ring, and performance monitoring registers.

- **Device 19:** Processor Performance Monitoring and Ring. Device 19 Function 0 contains the processor ring to PCI Express agent. Device 19, Function 1 contains the processor Ring to PCI Express performance monitoring registers. Device 19, Function 4 -6 contains the processor Ring to Intel QPI Link 0 and 1 Intel QPI agent ring and performance monitoring registers.

- **Device 22:** Processor Core Broadcast. Device 22 Function 1-2 contains the Caching agent broadcast configuration registers for the Memory Controller. Device 22 Function 0 contains the System Address Decode registers.

# 1.2 Configuration Register Rules

The Intel® Xeon® Processor E5 v2 product family supports the following configuration register types:

- PCI Configuration Registers (CSRs): CSRs are chipset specific registers that are located at PCI defined address space.

- Machine Specific Registers (MSRs): MSRs are machine specific registers that can be accessed by specific read and write instructions. It is OS ring 0 and BIOS accessible.

- Memory-mapped I/O registers: These registers are mapped into the system memory map as MMIO low or MMIO high. They are accessed by any code typically an OS driver running on the platform. This register space is introduced with the integration of some of the chipset functionality.

### 1.2.1 CSR Access

Configuration space registers are accessed via the well known configuration transaction mechanism defined in the PCI specification and this uses the bus:device:function number concept to address a specific device's configuration space. If initiated by a remote CPU, accesses to PCI configuration registers are achieved via NcCfgRd/Wr transactions on Intel QPI.

All configuration register accesses are accessed over Message Channel through the UBox but might come from a variety of different sources:

- Local cores

- Remote cores (over Intel QuickPath Interconnect)

- PECI or JTAG

Configuration registers ccan be read or written in Byte, WORD (16-bit), or DWORD (32bit) quantities. *Accesses larger than a DWORD to PCI Express configuration space will result in unexpected behavior.* All multi-byte numeric fields use "little-endian" ordering (that is, lower addresses contain the least significant parts of the field)..

### 1.2.1.1 PCI Bus Number

In the tables shown for IIO devices (0 - 7), the PCI Bus numbers are all marked as "Bus 0". This means that the actual bus number is variable depending on which socket is used. The specific bus number for all PCIe devices in the Intel® Xeon® Processor E5 v2

product family is specified in the CPUBUSNO register which exists in the I/O module's configuration space. Bus number is derived by the max bus range setting and processor socket number.

#### 1.2.1.2 Uncore Bus Number

In the tables shown for Uncore devices (8 - 19), the PCI Bus numbers are all marked as "bus 1". This means that the actual bus number is CPUBUSNO(1) where CPUBUSNO(1) is programmable by BIOS depending on which socket is used. The specific bus number for all PCIe devices in the Intel® Xeon® Processor E5 v2 product family is specified in the CPUBUSNO register.

### 1.2.1.3 Device Mapping

Each component in the processor is uniquely identified by a PCI bus address consisting of Bus Number, Device Number and Function Number. Device configuration is based on the PCI Type 0 configuration conventions. All processor registers appear on the PCI bus assigned for the processor socket. Bus number is derived by the max bus range setting and processor socket number.

#### Table 1-1. Functions Specifically Handled by the Processor (Sheet 1 of 3)

| Register Group                        | DID                                                                 | Device | Function | Comment                                        |

|---------------------------------------|---------------------------------------------------------------------|--------|----------|------------------------------------------------|

| DMI2                                  | E00h                                                                | 0      | 0        | x4 Link from Processor to PCH                  |

| PCI Express Root Port in DMI2<br>Mode | E01h                                                                | 0      | 0        | Device 0 will work as a x4 PCI Express<br>Port |

| PCI Express Root Port 2               | E04h,<br>E05h,<br>E06h,<br>E07h                                     | 2      | 0 -3     | x16, x8 or x4 max link width                   |

| PCI Express Root Port 3               | E08,<br>E09h,<br>EOAh,<br>E0Bh                                      | 3      | 0-3      | x16, x8 or x4 max link width                   |

| Core                                  | E28h                                                                | 5      | 0        | Address Map, VTd_Misc, System<br>Management    |

| Core                                  | E29h                                                                | 5      | 1        | Hot-Plug                                       |

| Core                                  | E2Ah                                                                | 5      | 2        | RAS, Control Status and Global Errors          |

| Core                                  | E2Ch                                                                | 5      | 4        | I/O APIC                                       |

| Crystal Beach DMA                     | E20h,<br>E21h,<br>E22h,<br>E23h,<br>E24h,<br>E25h,<br>E26h,<br>E27h | 4      | 0-7      | DMA Channel 0 to Channel 7                     |

| Crystal Beach DMA                     | E2Eh -<br>E2Fh                                                      | 4      | 0-1      | RAID 5/6                                       |

| Intel QPI Link 0                      | E80h                                                                | 8      | 0        | Intel QPI Link 0                               |

| Intel QPI Link 1                      | E90h                                                                | 9      | 0        | Intel QPI Link 1                               |

| Intel QPI Link Reut 0                 | E83h,<br>E84h                                                       | 8      | 3,4      | Intel QPI Link Reut 0                          |

| Intel QPI Link Reut 1                 | E93h,<br>E94h                                                       | 9      | 3,4      | Intel QPI Link Reut 1                          |

| Register Group                 | DID                                                                 | Device | Function | Comment                                     |

|--------------------------------|---------------------------------------------------------------------|--------|----------|---------------------------------------------|

| PCU                            | ECOh,<br>EC1h,<br>EC2h<br>EC3h<br>EC4h                              | 10     | 0-4      | Power Control Unit                          |

| UBOX                           | E1Eh                                                                | 11     | 0        | Scratchpad and Semaphores                   |

| UBOX                           | E7Dh                                                                | 11     | 2        | Scratchpad and Semaphores                   |

| UBOX                           | E1F                                                                 | 11     | 3        | Scratchpad and Semaphores                   |

| Caching Agent (CBo)            | EEOh,<br>EE2h,<br>EE4h,<br>EE6h,<br>EE8h,<br>EEAh,<br>EECh,<br>EEEh | 12     | 0-7      | Unicast Registers                           |

| Caching Agent (CBo)            | EE1h,<br>EE3h,<br>EE5h,<br>EE7h,<br>EE9h,<br>EEBh,<br>EEDh          | 13     | 0-6      | Unicast Registers                           |

| Caching Agent (CBo)            | EC8h                                                                | 22     | 0        | System Address Decoder                      |

| Caching Agent (CBo)            | EC9h,<br>ECAh                                                       | 22     | 1-2      | Broadcast Registers                         |

| Integrated Memory Controller 0 | EA8h                                                                | 15     | 0        | CPGC                                        |

| Integrated Memory Controller 0 | E71h                                                                | 15     | 1        | RAS Registers                               |

| Integrated Memory Controller 0 | EAAh,<br>EABh,<br>EACh,<br>EADh                                     | 15     | 2 -5     | Channel Target Address Decoder<br>Registers |

| Integrated Memory Controller 0 | EBO,<br>EB1,<br>EB4<br>EB5                                          | 16     | 0,1,4,5  | Channel 0-3 Thermal Registers               |

| Integrated Memory Controller 0 | EB2<br>EB3<br>EB6<br>EB7                                            | 16     | 2,3,6,7  | Channel 0-3 ERROR Registers                 |

| Integrated Memory Controller 0 | EBAh,<br>EBBh,<br>EBEh,<br>EBFh                                     | 17     | 2,3,6,7  | For 1 HA: DDRIO 0,1,2,3 Multicast           |

| Integrated Memory Controller 0 | EBCh,<br>EBDh                                                       | 17     | 4,5      | For 2 HA: DDRIO 0 & 1                       |

| Integrated Memory Controller 0 | EBEh,<br>EBFh                                                       | 17     | 6,7      | For 2 HA: DDRIO 0,1,Multicast               |

| Integrated Memory Controller 0 | ED8h,<br>ED9h,<br>EDAh,<br>EDBh,                                    | 31     | 0-3      | For 2 HA only: DDRIO 2 & 3                  |

| R2PCIe                         | E1Dh                                                                | 19     | 0        | R2PCIE                                      |

### Table 1-1. Functions Specifically Handled by the Processor (Sheet 2 of 3)

#### Table 1-1. Functions Specifically Handled by the Processor (Sheet 3 of 3)

| Register Group                     | DID           | Device | Function | Comment                                    |

|------------------------------------|---------------|--------|----------|--------------------------------------------|

| R2PCIe                             | E34h          | 19     | 1        | PCI Express Ring Performance<br>Monitoring |

| R3 Intel QPI Link 0 & 1Performance | E36h,<br>E37h | 19     | 5-6      | Intel QPI Ring Performance Monitoring      |

| R3 Intel QPI 0 & 1                 | E81h          | 19     | 4        | Intel QPI Ring Registers                   |

| R3 Intel QPI 0 & 1                 | 0x2           | 20     | 1        | Intel QPI Ring Registers                   |

For Intel Xeon Processor E5-2400 v2 product families, ignore Intel QPI Link 1 and Memory channel 0. For Intel Xeon processor E5-1600 v2 product family, Intel QPI ports 0 and 1 do not exist. Thus the associated devices and functions are not used or unavailable.

#### 1.2.1.4 Unimplemented Devices/Functions and Registers

Configuration reads to unimplemented functions and devices will return all ones emulating a master abort response. Note that there is no asynchronous error reporting that happens when a configuration read master aborts. Configuration writes to unimplemented functions and devices will return a normal response.

Software should not attempt or rely on reads or writes to unimplemented registers or register bits. Unimplemented registers should return all zeroes when read. Writes to unimplemented registers are ignored. For configuration writes to these register (require a completion), the completion is returned with a normal completion status (not master-aborted).

#### 1.2.1.5 Device Hiding

The Intel® Xeon® Processor E5 v2 product family provides a mechanism by which various PCI devices or functions within the unit can be hidden from the host configuration software; that is, all PCI configuration accesses to the devices' configuration space from Intel QPI will be master aborted. This mechanism is needed in cases where a device or function is not used or is available for use, because either the device is turned off or the device is not serving any meaningful purpose in a given platform configuration.

This hiding mechanism is implemented via the DEVHIDE register:

- Devices that are hidden from host configuration space via the DEVHIDE register are not hidden from the configuration space as seen from the JTAG/SMBus port of an IIO. All PCI devices are always visible via JTAG/SMBus.

- Devices or functions when turned off are always hidden (and not programmable to be unhidden) from host configuration space and also from PECI/JTAG.

- Devices that are not turned off, but are otherwise not used in a given platform configuration can be hidden from host configuration space by BIOS appropriately programming the DEVHIDE register.

- The only change DEVHIDE register makes is to abort Type0 configuration accesses to the device space itself.

### 1.2.2 MSR Access

Machine specific registers are architectural and only accessed by using specific ReadMSR/WriteMSR instructions. MSRs are always accessed as a naturally aligned 4 or 8 byte quantity.

This document will include error handling configuration and logging related MSRs for various functional blocks such as Cbo, HA, iMC, QPI, IIO, and so forth. For common IA-32 architectural MSRs, please refer to the *Intel® 64 and IA-32 Software Developer's Manual*.

## 1.2.3 Memory-Mapped I/O Registers

The PCI standard provides not only configuration space registers but also registers which reside in memory-mapped space. For PCI devices, this is typically where the majority of the driver programming occurs and the specific register definitions and characteristics are provided by the device manufacturer. Access to these registers are typically accomplished via CPU reads and writes to non-coherent (UC) or write-combining (WC) space.