# Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset

**Specification Update**

February 2011

**Notice:** Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

Document Number: 322170-017

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS OTHERWISE AGREED IN WRITING BY INTEL, THE INTEL PRODUCTS ARE NOT DESIGNED NOR INTENDED FOR ANY APPLICATION IN WHICH THE FAILURE OF THE INTEL PRODUCT COULD CREATE A SITUATION WHERE PERSONAL INJURY OR DEATH MAY OCCUR.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request. Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

This document contains information on products in the design phase of development.

All products, platforms, dates, and figures specified are preliminary based on current expectations, and are subject to change without notice. All dates specified are target dates, are provided for planning purposes only and are subject to change.

This document contains information on products in the design phase of development. Do not finalize a design with this information. Revised information will be published when the product is available. Verify with your local sales office that you have the latest datasheet before finalizing a design.

$I^2C$  is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $I^2C$  bus/protocol and was developed by Intel. Implementations of the  $I^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Code names featured are used internally within Intel to identify products that are in development and not yet publicly announced for release. Customers, licensees and other third parties are not authorized by Intel to use code names in advertising, promotion or marketing of any product or services and any such use of Intel's internal code names is at the sole risk of the user.

Intel and the Intel logo are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2011, Intel Corporation. All rights reserved.

# Contents

| Preface                                 | 7 |

|-----------------------------------------|---|

| Affected Documents/Related Documents    | 7 |

| Nomenclature                            | 7 |

| Summary Tables of Changes               | 8 |

| Codes Used in Summary Tables            |   |

| Stepping                                |   |

| Page                                    |   |

| Status                                  |   |

| Row                                     | 8 |

| Errata                                  | 9 |

| Specification Changes1                  | 0 |

| Specification Clarification1            | 0 |

| Documentation Changes1                  | 0 |

| Identification Information              | 2 |

| Markings1                               | 2 |

| PCH Device and Revision Identification1 | 3 |

| Errata                                  | 5 |

| Specification Changes                   | 6 |

| Specification Clarification             | 9 |

| Documentation Changes                   | 3 |

§

# **Revision History**

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Date              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| -001     | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | September 2009    |

| -002     | <ul> <li>Updated         <ul> <li>Identification Information Markings</li> <li>PCH Device and Revision Identification</li> <li>6-Errata: Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset Full-Speed USB Isochronous Packet Truncation</li> </ul> </li> <li>Added         <ul> <li>Errata: 7-Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset USB Port Stall with Bulk and Control Traffic, 8-Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset SATA SYNC Escape Erratum</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | January 7, 2010   |

| -003     | <ul> <li>Added         <ul> <li>Errata: 9 - Intel<sup>®</sup> P55, PM55, 3400, and 3420 Chipsets May Not Fully Initialize<br/>Intel<sup>®</sup> ME, 10 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset USB End of<br/>Frame When Retrying Packets Issue, 11 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400<br/>Series Chipset USB Transaction Priority Issue, 12 - Intel<sup>®</sup> H55 Express Chipset<br/>and Intel<sup>®</sup> 3420 Chipset May Report Incorrect Number of USB Ports, 13 - Intel<sup>®</sup><br/>HM55 Express Chipset May Report Incorrect Number of USB Ports</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | January 13, 2010  |

| -004     | <ul> <li>Added         <ul> <li>Errata: 14 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset HPET Writing<br/>Timing Issue, 15 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset USB<br/>Full-Speed Port Staggering</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | February 13, 2010 |

| -005     | <ul> <li>Added         <ul> <li>Errata: 16 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset USB Device May Slow or Hang, 17- Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset USB Low Speed Bulk/Control Transactions, 18- Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset May Not Detect Unsolicited SATA COMIINITs, 19- Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset and Intel<sup>®</sup> 5 Series Chipset SATA Hot Unplug.</li> <li>Specification Clarification: 1. GP_RST_SEL[95:0] Description Updated</li> </ul> </li> <li>Updated:         <ul> <li>Intel<sup>®</sup>QS57 Chipset High Definition Audio Device ID Updated</li> </ul> </li> </ul> | March 10, 2010    |

| -006     | Added<br>• Documentation Changes: 1. Correct Figure 8-2 S5 to S0 Timing Diagram<br>• Updated Errata 17 Removed Bulk Transtion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | April 14, 2010    |

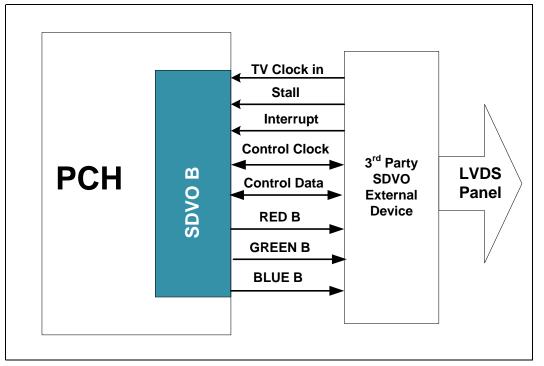

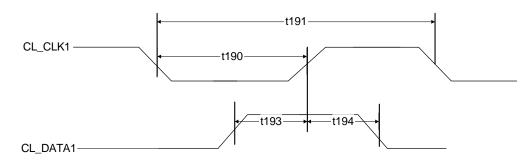

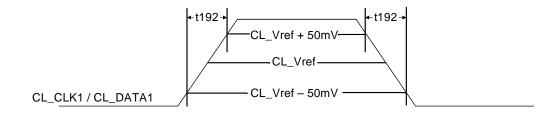

| -007     | <ul> <li>Added</li> <li>Documentation Changes: 2. Update Table 3-1 to include SPI_CSO#. 3. Add Tj Mobile<br/>Thermal Junction Operating Temperature limits in Table 8-1. 4. Add sections 5.27.2.9<br/>through 5.27.2.15 to section 5.27 PCH DisPlay Interface. 5. Remove Unit Interval DMI<br/>from Table 8-14</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | May 12, 2010      |

| -008     | Edited<br>• Corrected typographical error in Documentation Changes, item #4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | May 17, 2010      |

| -009     | <ul> <li>Added         <ul> <li>Errata: 20- Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset USB Missing ACK</li> <li>Updated:                 <ul> <li>Errata: 11- Intel<sup>®</sup> 5 / 3400 Series Chipset Family USB Classic Device Removal Issue</li> <li>Removed                     <ul></ul></li></ul></li></ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | June 9, 2010      |

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Date              |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| -010     | <ul> <li>Added         <ul> <li>Errata: 21 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset Serial ATA Revision 3.0 (SATA 6Gb/s) Device Detection , 22 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset PCI Express* Link Disable Bit.</li> </ul> </li> <li>Updated:         <ul> <li>Specification Clarification: 1- Host WOL Behavior Clarification.</li> <li>Documentation Changes: 1- Correct Table 5-58 PCH supported Audio formats over HDMI and DisplayPort*.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | July 14, 2010     |

| -011     | <ul> <li>Updated:         <ul> <li>Documentation Changes: 2 - Correct Table 8-8 DC Output Characteristics and<br/>Notes 1; 3 - Correct 21.1.2 HSFS-Hardware Sequencing Flash Status Register (SPI<br/>Memory Mapped Configuration Registers); 4 - Correct 21.4.2 HSFS—Hardware<br/>Sequencing Flash Status Register (GbE LAN Memory Mapped Configuration<br/>Registers)</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | August 11, 2010   |

| -012     | <ul> <li>Added         <ul> <li>Errata: 23 - Pixel Corruption Over Integrated LVDS Interface of Intel<sup>®</sup> 5 Series<br/>Chipset.</li> </ul> </li> <li>Updated:         <ul> <li>Specification Clarification: 2 - Display Port Clarification</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | September 8, 2010 |

| -013     | <ul> <li>Updated:         <ul> <li>Errata: 21 - Pixel Corruption Over Integrated LVDS Interface of Intel<sup>®</sup> 5 Series<br/>Chipset</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | October 13, 2010  |

| -014     | <ul> <li>Added         <ul> <li>Errata: 24- Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset Family High-speed USB Device False Disconnect.</li> <li>Specification Changes: 1 - SMLinkO Speed Change; 2 - VccVRM Min/Max Change</li> <li>Specification Clarification: 3 - PIRQ Sharing; 4 - t205 Vcc Reference; 5 - Table 2-27 Power and Ground Signals</li> <li>Documentation Changes: 5 - Correct 13.1.23 GEN1_DEC—LPC I/F Generic Decode Range 1 Register (LPC I/F—D31:F0); 6 - Correct Table 2-28 Functional Strap Definitions; 7 - Correct Table 9-4 Memory Decode Ranges from Processor Perspective; 8 - Correct 10.1.43 OIC—Other Interrupt Control Register; 9 - Miscellaneous Typographical and Omission Error Corrections; 10 - Update Table 2-8 USB Interface Signals; 11 - Update Note 2 of Table 9-1 PCI Devices and Functions; 12 - Correct 14.2.1 BMIC[P,S]—Bus Master IDE Command Register (D31:F2); 13 - Correct 15.2.1 BMIC[P,S]—Bus Master IDE Command Register (D31:F2); 14 - Update Table 4-1 PCH System Clock Inputs; 15 - Update Table 2-20 Clock Interface Signals; 16 - Display Interface Updates; 17 - Correct Table 2-20 Clock Interface Signals; 18 - Correct Table 1-3. Intel<sup>®</sup> 5 Series Chipset Mobile SKUs; 18 - Correct Table 1-3. Intel<sup>®</sup> 5 Series</li> </ul> </li> </ul> | November 10, 2010 |

| -015     | <ul> <li>Added         <ul> <li>Errata: 25- USB Isoch In Transfer Error Issue; 26- USB Full-Speed / Low-Speed Device Removal Issue; 27- USB Babble Detected with SW Overscheduling; 28-USB Low-Speed/Full-Speed EOP Issue; 29- USB PLL Control FSM Not Getting Reset on Global Reset; 30- Asynchronous Retries Prioritized Over Periodic Transfers; 31- Incorrect Data for LS or FS USB Periodic IN Transaction; 32- Intel<sup>®</sup> 5 Series and 3400 Series Chipset Family Delayed Periodic Traffic Timeout Issue.</li> <li>Specification Clarification: 6- EHCI Function Numbers; 7- PCI Express* Root Port Function Numbers; 8- t212 Measurement Clarification; 9- Wake Event Causes Update; 10- SGPIO Reference Clock Speed.</li> <li>Documentation Changes: 19- Controller Link Updates; 20- Miscellaneous Typographical Error Corrections II; 21- Remove note 11 on Table 3-3; 22- Remove VccpNAND on Table 8-3 and Table 8-4; 23- Section 8.2 Updates.</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                    | December 8, 2010  |

| -016     | <ul> <li>Update         <ul> <li>Errata: 14- Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset HPET Writing Timing Issue; 21 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset Serial ATA Revision 3.0 (SATA 6Gb/s) Device Detection</li> </ul> </li> <li>Added         <ul> <li>Specification Clarification: 11- I<sup>2</sup>C Block Read/Write Buffer</li> <li>Documentation Changes: 24- TEMP_ALERT# Muxing; 25- Causes of Host and Global Resets Update; 26- GPIO18 Toggling Note; 27- Pre-fetch Based Pause Bit Definition; 28- Register Corrections; 29- Display BDF Register Additions; 30-Miscellaneous Typographical Error Corrections III</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | January 12, 2011  |

| -017     | <ul> <li>Update         <ul> <li>Errata: 21 - Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset Serial ATA 6Gb/s Device Detection</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | February 16, 2011 |

§§

## Preface

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

## **Affected Documents/Related Documents**

| Title                                                                                    | Document<br>Number |

|------------------------------------------------------------------------------------------|--------------------|

| Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset Datasheet | 322169             |

## Nomenclature

**Errata** are design defects or errors. Errata may cause the behavior of the PCH to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present in all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

§

# **Summary Tables of Changes**

The following tables indicate the errata, specification changes, specification clarifications, or documentation changes which apply to the PCH product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. These tables uses the following notations:

## **Codes Used in Summary Tables**

## Stepping

|        | X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------|

|        | (No mark)       |                                                                                                               |

|        | or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| Page   |                 |                                                                                                               |

|        | (Page):         | Page location of item in this document.                                                                       |

| Status |                 |                                                                                                               |

|        | Doc:            | Document change or update will be implemented.                                                                |

|        | Plan Fix:       | This erratum may be fixed in a future stepping of the product.                                                |

|        | Fixed:          | This erratum has been previously fixed.                                                                       |

|        | No Fix:         | There are no plans to fix this erratum.                                                                       |

| D      |                 |                                                                                                               |

Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

| Erratum | Step | ping       | Chatura | EDDATA                                                                                                                                                                                                  |  |                                                            |  |  |

|---------|------|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------|--|--|

| Number  | B2   | <b>B</b> 3 | Status  | ERRATA                                                                                                                                                                                                  |  |                                                            |  |  |

| 1       | х    | х          | No Fix  | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset High-Speed USB Test J/Test K<br>Output Drive Level                                                                       |  |                                                            |  |  |

| 2       | х    | х          | No Fix  | Intel $^{\textcircled{B}}$ 5 Series Chipset and Intel $^{\textcircled{B}}$ 3400 Series Chipset High-Speed USB 2.0 Vhsoh                                                                                 |  |                                                            |  |  |

| 3       | х    | х          | No Fix  | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset 1.5 Gb/s & 3.0 Gb/s SATA Signal Voltage Level                                                                            |  |                                                            |  |  |

| 4       | Х    | Х          | No Fix  | Intel $^{\textcircled{R}}$ 5 Series Chipset and Intel $^{\textcircled{R}}$ 3400 Series Chipset SATA Low Power Device Detection                                                                          |  |                                                            |  |  |

| 5       | х    | х          | No Fix  | Intel $^{\ensuremath{\mathbb{R}}}$ 5 Series Chipset and Intel $^{\ensuremath{\mathbb{R}}}$ 3400 Series Chipset Intel $^{\ensuremath{\mathbb{R}}}$ HD Audio Interface Intermittently Does Not Play Sound |  |                                                            |  |  |

| 6       | х    |            | Fixed   | Intel $^{\ensuremath{\mathbb{R}}}$ 5 Series Chipset and Intel $^{\ensuremath{\mathbb{R}}}$ 3400 Series Chipset Full-Speed USB Isochronous Packet Truncation                                             |  |                                                            |  |  |

| 7       | х    | х          | No Fix  | ${\rm Intel}^{\circledast}$ 5 Series Chipset and ${\rm Intel}^{\circledast}$ 3400 Series Chipset USB Port Stall with Bulk and Control Traffic                                                           |  |                                                            |  |  |

| 8       | Х    | Х          | No Fix  | Intel $^{\ensuremath{\mathbb{R}}}$ 5 Series Chipset and Intel $^{\ensuremath{\mathbb{R}}}$ 3400 Series Chipset SATA SYNC Escape Erratum.                                                                |  |                                                            |  |  |

| 9       | х    |            | Fixed   | Intel $^{\ensuremath{\mathbb{R}}}$ P55, PM55, 3400, and 3420 Chipsets May Not Fully Initialize Intel $^{\ensuremath{\mathbb{R}}}$ Management Engine                                                     |  |                                                            |  |  |

| 10      | х    | х          | No Fix  | Intel $^{\ensuremath{\mathbb{R}}}$ 5 Series Chipset and Intel $^{\ensuremath{\mathbb{R}}}$ 3400 Series Chipset USB End of Frame When Retrying Packets Issue                                             |  |                                                            |  |  |

| 11      | Х    | Х          | No Fix  | Intel $^{\textcircled{B}}$ 5 / 3400 Series Chipset Family USB Classic Device Removal Issue                                                                                                              |  |                                                            |  |  |

| 12      | х    | х          | No Fix  | Intel <sup>®</sup> H55 Express Chipset and Intel <sup>®</sup> 3420 Chipset May Report Incorrect Number of USB Ports                                                                                     |  |                                                            |  |  |

| 13      | Х    | Х          | No Fix  | Intel <sup>®</sup> HM55 Express Chipset May Report Incorrect Number of USB Ports                                                                                                                        |  |                                                            |  |  |

| 14      | Х    | х          | No Fix  | Intel $^{\circledast}$ 5 Series Chipset and Intel $^{\circledast}$ 3400 Series Chipset HPET Writing Timing Issue                                                                                        |  |                                                            |  |  |

| 15      | Х    | Х          | No Fix  | ${\sf Intel}^{\circledast}$ 5 Series Chipset and ${\sf Intel}^{\circledast}$ 3400 Series Chipset USB Full-Speed Port Staggering                                                                         |  |                                                            |  |  |

| 16      | Х    | Х          | No Fix  | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset USB Devices May Slow or Hang                                                                                             |  |                                                            |  |  |

| 17      | х    | х          | No Fix  | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset USB Low Speed Control Transactions                                                                                       |  |                                                            |  |  |

| 18      | х    | х          | No Fix  | Intel $^{\it @}$ 5 Series Chipset and Intel $^{\it @}$ 3400 Series Chipset May Not Detect Unsolicited SATA COMINITs                                                                                     |  |                                                            |  |  |

| 19      | Х    | Х          | No Fix  | Intel $^{\circledast}$ 5 Series Chipset and Intel $^{\circledast}$ 3400 Series Chipset SATA Hot Unplug                                                                                                  |  |                                                            |  |  |

| 20      | Х    | Х          | No Fix  | Intel $^{\circledast}$ 5 Series Chipset and Intel $^{\circledast}$ 3400 Series Chipset USB Missing ACK                                                                                                  |  |                                                            |  |  |

| 21      | х    | х          | No Fix  | Intel $^{\ensuremath{\mathbb{R}}}$ 5 Series Chipset and Intel $^{\ensuremath{\mathbb{R}}}$ 3400 Series Chipset Serial ATA 6Gb/s Device Detection                                                        |  |                                                            |  |  |

| 22      | Х    | Х          | No Fix  | Intel $^{\ensuremath{\mathbb{R}}}$ 5 Series Chipset and Intel $^{\ensuremath{\mathbb{R}}}$ 3400 Series Chipset PCI Express* Link Disable Bit                                                            |  |                                                            |  |  |

| 23      | Х    | Х          | No Fix  | Pixel Corruption Over Integrated LVDS Interface of Intel <sup>®</sup> 5 Series Chipset                                                                                                                  |  |                                                            |  |  |

| 24      | х    | х          | No Fix  | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset Family High-speed USB Device False Disconnect                                                                            |  |                                                            |  |  |

| 25      | Х    | Х          | No Fix  | USB Isoch In Transfer Error Issue                                                                                                                                                                       |  |                                                            |  |  |

| 26      | Х    | Х          | No Fix  | USB Full-Speed / Low-Speed Device Removal Issue                                                                                                                                                         |  |                                                            |  |  |

| 27      | х    | Х          | No Fix  | USB Babble Detected with SW Overscheduling                                                                                                                                                              |  |                                                            |  |  |

| 28      | х    | х          | No Fix  | USB Low-Speed/Full-Speed EOP Issue                                                                                                                                                                      |  |                                                            |  |  |

| 29      | х    | Х          | No Fix  | USB PLL Control FSM Not Getting Reset on Global Reset                                                                                                                                                   |  |                                                            |  |  |

| 30      | х    | х          | No Fix  | Asynchronous Retries Prioritized Over Periodic Transfers                                                                                                                                                |  | x Asynchronous Retries Prioritized Over Periodic Transfers |  |  |

| 31      | х    | х          | No Fix  | Incorrect Data for LS or FS USB Periodic IN Transaction                                                                                                                                                 |  |                                                            |  |  |

| 32      | Х    | Х          | No Fix  | Intel <sup>®</sup> 5 Series and 3400 Series Chipset Family Delayed Periodic Traffic Timeout Issue                                                                                                       |  |                                                            |  |  |

# **Specification Changes**

| Spec<br>Change | Step | ping       | SPECIFICATION CHANGES |  |  |

|----------------|------|------------|-----------------------|--|--|

| Number         | B2   | <b>B</b> 3 | SI LOTTORTON ONANOLS  |  |  |

| 1              | Х    | Х          | SMLink0 Speed Change  |  |  |

| 2              | Х    | Х          | VccVRM Min/Max Change |  |  |

## **Specification Clarification**

| No. | Document<br>Revision | SPECIFICATION CLARIFICATIONS           |  |  |  |

|-----|----------------------|----------------------------------------|--|--|--|

| 1   | 003                  | Host WOL Behavior Clarification        |  |  |  |

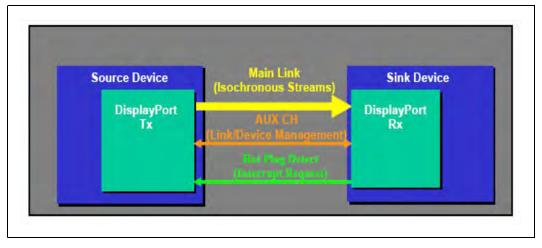

| 2   | 003                  | Display Port Clarification             |  |  |  |

| 3   | 003                  | PIRQ Sharing                           |  |  |  |

| 4   | 003                  | t205 Vcc Reference                     |  |  |  |

| 5   | 003                  | ble 2-27 Power and Ground Signals      |  |  |  |

| 6   | 003                  | HCI Function Numbers                   |  |  |  |

| 7   | 003                  | CI Express* Root Port Function Numbers |  |  |  |

| 8   | 003                  | t212 Measurement Clarification         |  |  |  |

| 9   | 003                  | Wake Event Causes Update               |  |  |  |

| 10  | 003                  | SGPIO Reference Clock Speed            |  |  |  |

## Documentation Changes (Sheet 1 of 2)

| No. | Document<br>Revision | DOCUMENTATION CHANGES                                                                                         |  |  |  |

|-----|----------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | 003                  | Correct Table 5-58 PCH supported Audio formats over HDMI and DisplayPort*                                     |  |  |  |

| 2   | 003                  | Correct Table 8-8 DC Output Characteristics and Note 1                                                        |  |  |  |

| 3   | 003                  | Correct 21.1.2 HSFS-Hardware Sequencing Flash Status Register (SPI Memory Mapped Configuration Registers)     |  |  |  |

| 4   | 003                  | Correct 21.4.2 HSFS—Hardware Sequencing Flash Status Register (GbE LAN Memory Mapped Configuration Registers) |  |  |  |

| 5   | 003                  | Correct 13.1.23 GEN1_DEC—LPC I/F Generic Decode Range 1 Register (LPC I/F—D31:F0)                             |  |  |  |

| 6   | 003                  | Correct Table 2-28 Functional Strap Definitions                                                               |  |  |  |

| 7   | 003                  | Correct Table 9-4 Memory Decode Ranges from Processor Perspective                                             |  |  |  |

| 8   | 003                  | Correct 10.1.43 OIC—Other Interrupt Control Register                                                          |  |  |  |

| 9   | 003                  | Miscellaneous Typographical and Omission Error Corrections                                                    |  |  |  |

| 10  | 003                  | Update Table 2-8 USB Interface Signals                                                                        |  |  |  |

| 11  | 003                  | Update Note 2 of Table 9-1 PCI Devices and Functions                                                          |  |  |  |

| 12  | 003                  | Correct 14.2.1 BMIC[P,S]—Bus Master IDE Command Register (D31:F2)                                             |  |  |  |

| 13  | 003                  | Correct 15.2.1 BMIC[P,S]—Bus Master IDE Command Register (D31:F5)                                             |  |  |  |

| 14  | 003                  | Update Table 4-1 PCH System Clock Inputs                                                                      |  |  |  |

| 15  | 003                  | Update Table 2-20 Clock Interface Signals                                                                     |  |  |  |

| 16  | 003                  | Display Interface Updates                                                                                     |  |  |  |

| No. | Document<br>Revision | DOCUMENTATION CHANGES                                               |  |  |  |

|-----|----------------------|---------------------------------------------------------------------|--|--|--|

| 17  | 003                  | Correct Table 1-4. Intel <sup>®</sup> 5 Series Chipset Mobile SKUs  |  |  |  |

| 18  | 003                  | Correct Table 1-3. Intel <sup>®</sup> 5 Series Chipset Desktop SKUs |  |  |  |

| 19  | 003                  | ntroller Link Updates                                               |  |  |  |

| 20  | 003                  | iscellaneous Typographical Error Corrections II                     |  |  |  |

| 21  | 003                  | Remove note 11 on Table 3-3                                         |  |  |  |

| 22  | 003                  | Remove VccpNAND on Table 8-3 and Table 8-4                          |  |  |  |

| 23  | 003                  | Section 8.2 Updates                                                 |  |  |  |

# Documentation Changes (Sheet 2 of 2)

§

# **Identification Information**

# Markings

| PCH<br>Stepping | S-Spec | Top Marking | Notes                           |  |

|-----------------|--------|-------------|---------------------------------|--|

| B2              | SLGWN  | 82PM55      | Intel <sup>®</sup> PM55 Chipset |  |

| B2              | SLGWV  | 82P55       | Intel <sup>®</sup> P55 Chipset  |  |

| B2              | SLGWX  | 3400        | Intel <sup>®</sup> 3400 Chipset |  |

| B2              | SLGWW  | 3420        | Intel <sup>®</sup> 3420 Chipset |  |

| B3              | SLGZQ  | 82QM57      | Intel® QM57 Chipset             |  |

| B3              | SLGZR  | 82HM57      | Intel <sup>®</sup> H57 Chipset  |  |

| B3              | SLGZS  | 82HM55      | Intel <sup>®</sup> HM55 Chipset |  |

| B3              | SLGZW  | 82Q57       | Intel <sup>®</sup> Q57 Chipset  |  |

| B3              | SLGZL  | 82H57       | Intel <sup>®</sup> H57 Chipset  |  |

| B3              | SLGZX  | 82H55       | Intel <sup>®</sup> H55 Chipset  |  |

| B3              | SLH25  | 3520        | Intel <sup>®</sup> 3420 Chipset |  |

| B3              | SLGZY  | 3450        | Intel <sup>®</sup> 3450 Chipset |  |

| B3              | SLGZV  | 82QS57      | Intel <sup>®</sup> QS57 Chipset |  |

| B3              | SLH23  | 82PM55      | Intel <sup>®</sup> PM55 Chipset |  |

| B3              | SLH24  | 82P55       | Intel <sup>®</sup> P55 Chipset  |  |

I

## PCH Device and Revision Identification

The Revision ID (RID) is traditionally an 8-bit register located at the offset 08h in the PCI header of every PCI device and function. The assigned value is based on the product's stepping.

# Intel $^{\$}$ 5 Series Chipset and Intel $^{\$}$ 3400 Series Chipset Device and Revision ID Table (Sheet 1 of 2)

| Device<br>Function | Description | Dev ID <sup>1</sup> | B2<br>Rev ID | B3<br>Rev ID | Comments                                                    |

|--------------------|-------------|---------------------|--------------|--------------|-------------------------------------------------------------|

|                    |             | 3B02h               | 05h          | 06h          | Intel <sup>®</sup> P55 Chipset                              |

|                    |             | 3B03h               | 05h          | 06h          | Intel <sup>®</sup> PM55 Chipset                             |

|                    |             | 3B06h               | n/a          | 06h          | Intel <sup>®</sup> H55 Chipset                              |

|                    |             | 3B07h               | n/a          | 06h          | Intel <sup>®</sup> QM57 Chipset                             |

|                    |             | 3B08h               | n/a          | 06h          | Intel <sup>®</sup> H57 Chipset                              |

| D31:F0             | LPC         | 3B09h               | n/a          | 06h          | Intel <sup>®</sup> HM55 Chipset                             |

| 031.F0             | LFC         | 3B0Ah               | n/a          | 06h          | Intel <sup>®</sup> Q57 Chipset                              |

|                    |             | 3B0Bh               | n/a          | 06h          | Intel <sup>®</sup> HM57 Chipset                             |

|                    |             | 3B0Fh               | n/a          | 06h          | Intel <sup>®</sup> QS57 Chipset                             |

|                    |             | 3B12h               | 05h          | n/a          | Intel <sup>®</sup> 3400 Chipset                             |

|                    |             | 3B14h               | 05h          | 06h          | Intel <sup>®</sup> 3420 Chipset                             |

|                    |             | 3B16h               | n/a          | 06h          | Intel <sup>®</sup> 3450 Chipset                             |

|                    |             | 3B20h               | 05h          | 06h          | Desktop: Non-AHCI and Non-RAID Mode<br>(Ports 0, 1, 2, 3)   |

|                    |             | 3B21h               | 05h          | 06h          | Desktop: Non-AHCI and Non-RAID Mode<br>(Ports 0 and 1)      |

|                    |             | 3B22h               | 05h          | 06h          | Desktop: AHCI (Ports 0-5)                                   |

|                    |             | 3B23h               | 05h          | 06h          | Desktop: AHCI (Ports 0, 1, 4 and 5)                         |

| D31:F2             | SATA        | 3B25h               | 05h          | 06h          | Desktop RAID: 0/1/5/10                                      |

| 031.12             | SAIA        | 3B28h               | 05h          | 06h          | Mobile: Non-AHCI and Non-RAID Mode<br>(Ports 0, 1, 4 and 5) |

|                    |             | 3B29h               | 05h          | 06h          | Mobile: AHCI (Ports 0, 1, 4 and 5)                          |

|                    |             | 3B2Ch               | 05h          | 06h          | Mobile: RAID: 0/1/5/10                                      |

|                    |             | 3B2Eh               | 05h          | 06h          | Mobile: Non-AHCI and Non-RAID Mode<br>(Ports 0, 1, 2, 3)    |

|                    |             | 3B2Fh               | 05h          | 06h          | Mobile: AHCI (Ports 0-5)                                    |

# Intel $^{\mbox{\tiny 8}}$ 5 Series Chipset and Intel $^{\mbox{\tiny 8}}$ 3400 Series Chipset Device and Revision ID Table (Sheet 2 of 2)

| Device<br>Function | Description                                 | Dev ID <sup>1</sup> | B2<br>Rev ID | B3<br>Rev ID | Comments                                               |

|--------------------|---------------------------------------------|---------------------|--------------|--------------|--------------------------------------------------------|

| D31:F5             | SATA                                        | 3B26h               | 05h          | 06h          | Desktop: Non-AHCI and Non-RAID Mode<br>(Ports 4 and 5) |

| D31:F5             | SATA                                        | 3B2Dh               | 05h          | 06h          | Mobile: Non-AHCI and Non-RAID Mode<br>(Ports 4 and 5)  |

| D31:F3             | SMBus                                       | 3B30h               | 05h          | 06h          |                                                        |

| D31:F6             | Thermal                                     | 3B32h               | 05h          | 06h          |                                                        |

| D30:F0             | DMI to PCI Bridge                           | 244Eh               | A5h          | A6h          | Desktop                                                |

| D30:F0             | DMI to PCI Bridge                           | 2448h               | A5h          | A6h          | Mobile                                                 |

| D29:F0             | USB EHCI #1                                 | 3B34h               | 05h          | 06h          |                                                        |

| D26:F0             | USB EHCI #2                                 | 3B3Ch               | 05h          | 06h          |                                                        |

| D27:F0             | Intel High Definition<br>Audio              | 3B56h               | 05h          | 06h          |                                                        |

| D27:F0             | Intel <sup>®</sup> High<br>Definition Audio | 3B57h               | 05h          | 06h          | Intel <sup>®</sup> QS57 Chipset Only                   |

| D28:F0             | PCI Express* Port 1                         | 3B42h               | 05h          | 06h          |                                                        |

| D28:F1             | PCI Express Port 2                          | 3B44h               | 05h          | 06h          |                                                        |

| D28:F2             | PCI Express Port 3                          | 3B46h               | 05h          | 06h          |                                                        |

| D28:F3             | PCI Express Port 4                          | 3B48h               | 05h          | 06h          |                                                        |

| D28:F4             | PCI Express Port 5                          | 3B4Ah               | 05h          | 06h          |                                                        |

| D28:F5             | PCI Express Port 6                          | 3B4Ch               | 05h          | 06h          |                                                        |

| D28:F6             | PCI Express Port 7                          | 3B4Eh               | 05h          | 06h          |                                                        |

| D28:F7             | PCI Express Port 8                          | 3B50h               | 05h          | 06h          |                                                        |

| D25:F0             | LAN <sup>3</sup>                            | 3B41h               | 05h          | 06h          |                                                        |

| D22:F0             | Intel MEI #1                                | 3B64h               | 05h          | 06h          |                                                        |

| D22:F1             | Intel MEI #2                                | 3B65h               | 05h          | 06h          |                                                        |

| D22:F2             | IDE-R                                       | 3B66h               | 05h          | 06h          |                                                        |

| D22:F3             | КТ                                          | 3B67h               | 05h          | 06h          |                                                        |

#### NOTES:

1. The PCH contains two SATA controllers. The SATA Device ID is dependant upon which SATA mode is selected by BIOS and what RAID capabilities exist in the SKU.

The SATA RAID Controller Device ID may reflect a different value based on Bit 7 of D31:F2:Offset 9Ch.

LAN Device ID is loaded from EEPROM. If EEPROM contains either 0000h or FFFFh in the Device ID location, then 3B41h is used. Refer to the appropriate Intel GbE Physical Layer Transceiver (PHY) Datasheet for LAN Device IDs.

## Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset High-Speed USB Test J/Test K Output Drive Level 1.

Pre-emphasis is not disabled on high-speed USB ports during Test J/Test K. Problem:

J and K DC voltage levels may exceed USB 2.0  $\rm V_{\rm HSOH}-MAX$  and  $\rm V_{\rm HSOL}-MAX$  during Test J/Test K testing and may not meet the USB 2.0 specification. Implication:

Workaround: Clear bit 1 of the USB Initialization Registers [0-13] prior to enabling Test J/Test K mode using a memory editing tool. This bit must be set back to 1 for each port after Test J/Test K testing is complete.

| Port | Offset: RCBA +<br>Offset: |

|------|---------------------------|

| 0    | 3500h                     |

| 1    | 3504h                     |

| 2    | 3508h                     |

| 3    | 350Ch                     |

| 4    | 3510h                     |

| 5    | 3514h                     |

| 6    | 3518h                     |

| 7    | 351Ch                     |

| 8    | 3520h                     |

| 9    | 3524h                     |

| 10   | 3528h                     |

| 11   | 352Ch                     |

| 12   | 3530h                     |

| 13   | 3534h                     |

Status:

No Fix. For steppings affected, see the Summary Table of Changes.

#### Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset High-Speed 2. USB 2.0 V<sub>hsoh</sub>

High-Speed USB 2.0 V<sub>hsoh</sub> may not meet the USB 2.0 Specification. Problem:

- The maximum expected  $V_{\text{hsoh}}$  is 495 mV.

Some motherboards may exceed specification limits during USB-IF compliance testing. Implication: Workaround: None.

Status: No Fix. For steppings affected, see the Summary Table of Changes.

# 3. Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset 1.5 Gb/s & 3.0 Gb/s SATA Signal Voltage Level

- Problem: The Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset 1.5 Gb/s & 3.0 Gb/s SATA transmit buffers have been designed to maximize performance and robustness over a variety of routing scenarios. As a result, the Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset SATA 1.5 Gb/s & 3.0 Gb/s (Gen1i, Gen1m, Gen2i, and Gen2m) transmit signaling voltage levels may exceed the maximum motherboard TX connector and device RX connector voltage specifications (section 7.2.1 of the Serial ATA Specification, rev 2.5).

- Implication: None Known.

Workaround: None.

Status: No Fix. For steppings affected, see the Summary Table of Changes.

## 4. Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset SATA Low Power Device Detection

- Problem: Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset SATA Low Power Device Detection (SLPD) may not recognize, or may falsely detect, a SATA hot-plug event during a Partial or Slumber Link Power Management (LPM) state.

- Implication: On Systems which enable LPM, when a SATA device attached to the Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset is configured as External or hot-plug capable, one of the following symptoms may occur:

- <u>Symptom #1</u>: A hot-plug or External SATA device removal which is not detected results in the OS and Intel<sup>®</sup> Matrix Storage Manager/Intel<sup>®</sup> Rapid Storage Technology console falsely reporting the device present, or incorrectly identifying an eSATA device.

- <u>Symptom#2</u>: A false hot-plug removal detection may occur resulting in OS boot hang or ODD media playback hang

- Workaround: A driver workaround is available.

- Status: No Fix. For steppings affected, see the Summary Table of Changes.

- 5. Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset Intel<sup>®</sup> HD Audio Interface Intermittently Does Not Play Sound

- Problem: The Intel<sup>®</sup> 5 Series Chipset and Intel<sup>®</sup> 3400 Series Chipset Intel<sup>®</sup> HD Audio controller logic may not be gated by DMI L1 entry.

- Implication: Systems may intermittently not play sound on the Intel HD Audio interface Following a DMI L1 exit.

- Workaround: BIOS workaround available.

- Status: No Fix. For steppings affected, see the Summary Table of Changes.

| 6.           | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset Full-Speed USB Isochronous Packet Truncation                                                                                                          |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | Full-Speed isochronous-out transactions with multi-frame packets may be truncated, in the presence of Full or Low-Speed USB asynchronous transactions.                                                                               |

|              | <ul> <li>For this to occur, two devices, one performing Full-Speed isochronous-out<br/>transactions and one performing asynchronous transactions must be connected to<br/>the same USB controller (Ports 0-7 and 8-13).</li> </ul>   |

| Implication: | In the case of a USB audio device this issue may result in no audible impact or audible artifacts such as pops and clicks.                                                                                                           |

| Note:        |                                                                                                                                                                                                                                      |

|              | <ul> <li>High-Speed and Low-Speed USB devices are not impacted by this issue.</li> </ul>                                                                                                                                             |

|              | <ul> <li>Only devices supporting Full-Speed isochronous-out transactions that Intel is aware<br/>of are audio devices, such as sound adapters, speakers, and headphones.</li> </ul>                                                  |

|              | <ul> <li>Intel has only observed the issue when a Full-Speed audio devices and Full-Speed<br/>USB web camera are connected to the same USB controller.</li> </ul>                                                                    |

| Workaround:  | None.                                                                                                                                                                                                                                |

| Status:      | Fixed For steppings affected, see the Summary Table of Changes.                                                                                                                                                                      |

| 7.           | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset USB Port Stall with Bulk and Control Traffic                                                                                                          |

| Problem:     | When a single USB bulk device is active on an EHCI controller, and the device has pending control and bulk traffic the PCH may not be able to resolve which traffic type is a priority and the associated with the device may stall. |

|              | <ul> <li>The processor must be in C0 for an extended period of time such as when Cx states<br/>are disabled, or if system traffic prevents the system from leaving C0.</li> </ul>                                                    |

| Implication: | The USB device may appear unresponsive. If Cx states are enabled the device may recover a short time later.                                                                                                                          |

| Note:        | Intel has only observed this failure on a limited number of devices. Failure only occurs if software associated with a USB device programs the Nak Count Reload bits defined in the EHCI Specification for USB Rev 1.0 to 0.         |

| Workaround:  | A BIOS code change has been identified and may be implemented as a workaround for this erratum.                                                                                                                                      |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                    |

| 8.           | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset SATA SYNC Escape Erratum                                                                                                                              |

| Problem:     | When SYNC Escape by a SATA device occurs on a D2H FIS, the PCH does not set the PxIS.IFS bit to '1.' This deviates from section 6.1.9 of the Rev 1.3 Serial ATA Advanced Host Controller Interface (AHCI).                           |

| Implication: | There is no known observable impact. Instead of detecting the IFS bit, software will detect a timeout error caused by the SYNC escape and then respond.                                                                              |

| Workaround:  | None.                                                                                                                                                                                                                                |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                    |

| 9.           | Intel <sup>®</sup> P55, PM55, 3400, and 3420 Chipsets May Not Fully Initialize<br>Intel <sup>®</sup> ME                                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | Some Intel P55, PM55, 3400, and 3420 based systems with Intel ME Ignition 6.0.0.1126 PV firmware may fail to correctly initialize the Intel ME subsystem during boot at colder temperatures.                                                |

| Implication: | Failures may occur during BIOS update. Systems fans may run continuously at full speed and the system may have increased power consumption.                                                                                                 |

| Workaround:  | A BIOS code change has been identified and may be implemented as a workaround for this erratum.                                                                                                                                             |

| Status:      | Fixed. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                            |

| 10.          | Intel <sup>®</sup> 5 Series Chipset and Intel <sup>®</sup> 3400 Series Chipset USB End of Frame When Retrying Packets Issue                                                                                                                 |

| Problem:     | If the PCH encounters a Full-Speed or Low-Speed USB transaction with errors, the PCH may retry the transaction without considering if the transaction can finish before the end of the current frame.                                       |

| Implication: | The implication is dependant on the USB device. The PCH will attempt to recover per error handling specified in Section 4.5.2 of the USB Specification 2.0. The device may hang and require cycle to resume normal functionality.           |

| Note:        | Intel has only observed this behavior on a limited number of USB devices. The implication only occurs if a USB device does not correctly respond to error handling as specified Section 4.5.2 of the USB Specification 2.0.                 |

| Workaround:  | None.                                                                                                                                                                                                                                       |

| Status:      | No Fix. For steppings affected, see the Summary Table of Changes.                                                                                                                                                                           |

| 11.          | Intel® 5 / 3400 Series Chipset Family USB Classic Device Removal<br>Issue                                                                                                                                                                   |

| Problem:     | If two or more USB Full-Speed / Low-Speed devices are connected to the same USB controller, the devices are not suspended, and one device is removed, one or more of the devices remaining in the system may be affected by the disconnect. |

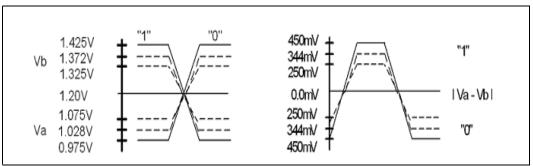

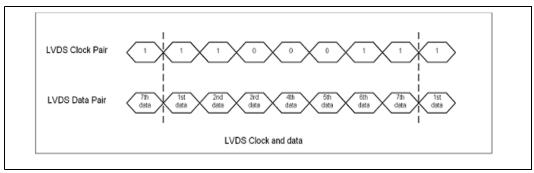

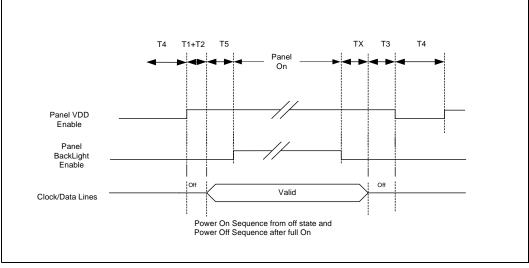

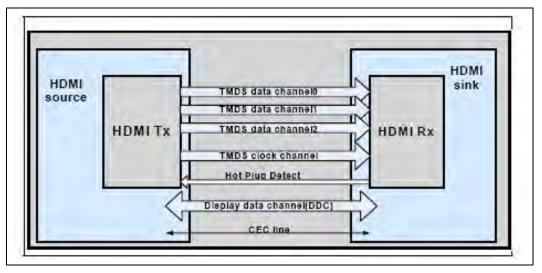

| Implication: | The implication is device dependant. A device may experience a delayed transaction, stall and be recovered via software, or stall and require a reset such as a hot plug to resume normal functionality.                                    |