## ISP2312 Designer's Guide

Dual 2-Gb Fibre Channel to 133-MHz PCI-X Controller

83312-508-00 E Page i

Information furnished in this manual is believed to be accurate and reliable. However, QLogic Corporation assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use. QLogic Corporation reserves the right to change product specifications at any time without notice. Applications described in this document for any of these products are for illustrative purposes only. QLogic Corporation makes no representation nor warranty that such applications are suitable for the specified use without further testing or modification. QLogic Corporation assumes no responsibility for any errors that may appear in this document.

No part of this document may be copied nor reproduced by any means, nor translated nor transmitted to any magnetic medium without the express written consent of QLogic Corporation.

636181-1 and AMP are trademarks or registered trademarks of AMP Incorporated.

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc

ApsimRLGC is a copyright and trademark of Applied Simulation Technology, Inc.

Atmel is a trademark of Atmel Corporation.

Cypress is a trademark of Cypress Semiconductor Corporation.

EPSON, the EPSON logo, and EPSON Stylus are registered trademarks of Seiko Epson Corporation (SEC).\

Fairchild is a trademark of Fairchild Semiconductor.

Microchip is a registered trademark of Microchip Technology Incorporated.

Micron is a registered trademark of Micron Technology, Inc.

Molex is a trademark of Molex Incorporated.

QLogic is a trademark of QLogic Corporation.

Samsung is a trademark of Samsung Electronics Co. LTD.

Siemens is a trademark of Siemens AG 1999, D-80312 München.

ST is a registered trademark of STMicroelectronics Group.

All other brand and product names are trademarks or registered trademarks of their respective owners.

### Document Revision History

Rev. A release, 4/4/01, chip affected: ISP2312 (2405236)

Rev. B update, 5/31/01, chip affected: ISP2312 (2405236)

Rev. C update, 6/27/01, chip affected: ISP2312 (2405236)

Rev. D update, 4/19/02, chips affected: ISP2312-ES1 (2405236), ISP2312-ES2 (2405311, 2405322)

Rev. E update, 8/1/03, chips affected: ISP2312-ES1 (2405236), ISP2312-ES2 (2405311, 2405322)

| Changes                                                                                                                                                                                                                                                                                                                                            | Document Sections Affected |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Electrical characteristics: Changed maximum power dissipation (Pmax) value. Changed maximum case temperature @Pmax (Tc) value. Provided measurements for IDD (previously preliminary estimates). Removed statement "Capacitance in and out (CIN, COUT) is 10 pf maximum for all pins." DC characteristics: removed SSTL parameter for VOH and VOL. | 2.4                        |

| Pins RADDR18–20_1 and RADDR18–20_2 can be used only for debug purposes; they can no longer be used an SRAM chip select.                                                                                                                                                                                                                            | 3.2.2                      |

| NCVS pin is no longer used as a sense input during power-up reset.                                                                                                                                                                                                                                                                                 | 3.2.4                      |

| GPIO_1[0] and GPIO_2[0] can no longer be configured as input pins for RISC debugging. GPIO_1[1] and GPIO_2[1] can no longer be configured as output pins for RISC debugging.                                                                                                                                                                       | 3.2.7, 6.7.13              |

Page ii 83312-508-00 E

| programmed to control the LEDs on the HBA. These pins are controlled by the RISC firmware to indicate I/O activity and status information. To maintain firmware compatibility, these signals must not be used for any other purpose.  The REFCLK2 pin is reserved; it no longer provides a clock for the internal ISP2312 logic.  Corrected PCI interface signal connection diagrams to show PCIXCAP.  Corrected PCI of 4-bit addressing with Dual Address Cycle command.  PCI Vendor ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI Device ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI-X Status register: corrected description of Function Number bits (bits 2–0).  ISP Control/Status register is accessible from the RISC processor (documentation error).  GPIOD register: The RISC processor and host driver must coordinate access to this register.  Changed SRAM connection configurations.  Changed SRAM connection configurations.  The RISC interface can be implemented using the additional SRAM configurations of 1M×18 and 2M×18.  Changed SRAM connection configurations.  The following locations are no longer used for system vendor and device ID 73h Function 1/port 2: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID Added function/port information illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3-2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  Updated schematics. | For QLogic HBA designs, the GPIO_1[0, 7–6] and GPIO_2[0, 7–6] pins are                                                                                                                                                | 3.2.7, 6.7.13             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| ISP2312 logic.  Corrected PCI interface signal connection diagrams to show PCIXCAP.  Corrected PCI 64-bit addressing with Dual Address Cycle command.  PCI Vendor ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI Device ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI-X Status register: corrected description of Function Number bits (bits 2–0).  ISP Control/Status register is accessible from the RISC processor (documentation error).  GPIOD register: The RISC processor and host driver must coordinate access to this register.  The RISC interface can be implemented using the additional SRAM configurations of 11M×18 and 21M×18.  Changed SRAM connection configurations.  RISC SRAM supports loading for only one SRAM device.  SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts).  Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDs for each function:  Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.                                                                                                                                                                 | programmed to control the LEDs on the HBA. These pins are controlled by the RISC firmware to indicate I/O activity and status information. To maintain firmware compatibility, these signals must not be used for any | 5.2.7, 0.7.15             |

| Corrected PCI 64-bit addressing with Dual Address Cycle command.  PCI Vendor ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI Device ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI-X Status register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI-X Status register: corrected description of Function Number bits (bits 2–0).  ISP Control/Status register is accessible from the RISC processor (documentation error).  GPIOD register: The RISC processor and host driver must coordinate access to this register.  The RISC interface can be implemented using the additional SRAM configurations of 1M×18 and 2M×18.  Changed SRAM connection configurations.  RISC SRAM supports loading for only one SRAM device.  SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts).  Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDS for each function:  Function 0/port 1: system vendor ID 72h, system device ID 73h  Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.                                                                                                             |                                                                                                                                                                                                                       | 3.2.7, removed 5.3, 5.3.2 |

| PCI Vendor ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI Device ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI-X Status register: corrected description of Function Number bits (bits 2–0).  ISP Control/Status register is accessible from the RISC processor (documentation error).  GPIOD register: The RISC processor and host driver must coordinate access to this register.  The RISC interface can be implemented using the additional SRAM configurations of 11M×18 and 2M×18.  Changed SRAM connection configurations.  RISC SRAM supports loading for only one SRAM device.  SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts).  Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDS for each function: Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.                                                                                                                                                                                                                                                                                                                          | Corrected PCI interface signal connection diagrams to show PCIXCAP.                                                                                                                                                   | 6.2.1, 6.2.2, 6.2.3       |

| from an external Serial EEPROM when the NVCS pin is pulled up.  PCI Device ID register: The value in this register can no longer be loaded from an external serial EEPROM when the NVCS pin is pulled up.  PCI-X Status register: corrected description of Function Number bits (bits 2–0).  ISP Control/Status register is accessible from the RISC processor (documentation error).  GPIOD register: The RISC processor and host driver must coordinate access to this register.  The RISC interface can be implemented using the additional SRAM configurations of 1M×18 and 2M×18.  Changed SRAM connection configurations.  RISC SRAM supports loading for only one SRAM device.  SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts).  Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDS for each function:  Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.                                                                                                                                                                                                                                                                                                                                                                                                     | Corrected PCI 64-bit addressing with Dual Address Cycle command.                                                                                                                                                      | 6.4.1                     |

| from an external serial EEPROM when the NVCS pin is pulled up.  PCI-X Status register: corrected description of Function Number bits (bits 2–0).  ISP Control/Status register is accessible from the RISC processor (documentation error).  GPIOD register: The RISC processor and host driver must coordinate access to this register.  The RISC interface can be implemented using the additional SRAM configurations of 1M×18 and 2M×18.  Changed SRAM connection configurations.  RISC SRAM supports loading for only one SRAM device.  SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts).  Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDs for each function:  Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                       |                           |

| (bits 2–0).  ISP Control/Status register is accessible from the RISC processor (documentation error).  GPIOD register: The RISC processor and host driver must coordinate access to this register.  The RISC interface can be implemented using the additional SRAM configurations of 1M×18 and 2M×18.  Changed SRAM connection configurations.  RISC SRAM supports loading for only one SRAM device.  SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts).  Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDs for each function:  Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                       |                           |

| (documentation error).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                       | 6.6.20.4                  |

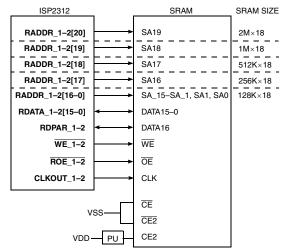

| access to this register.  The RISC interface can be implemented using the additional SRAM configurations of 1M×18 and 2M×18.  Changed SRAM connection configurations. RISC SRAM supports loading for only one SRAM device. SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts). Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDs for each function: Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                       | 6.7.3, A.3                |

| configurations of 1M×18 and 2M×18.  Changed SRAM connection configurations. RISC SRAM supports loading for only one SRAM device. SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts). Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDs for each function: Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                       | 6.7.13                    |

| RISC SRAM supports loading for only one SRAM device. SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts). Updated recommended SRAM devices.  The following locations are no longer used for system vendor and device IDs for each function: Function 0/port 1: system vendor ID 72h, system device ID 73h Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                       | 7.1                       |

| for each function:     Function 0/port 1: system vendor ID 72h, system device ID 73h     Function 1/port 2: system vendor ID F2h, system device ID F3h  Added function/port information to PCI subsystem ID and subsystem vendor ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RISC SRAM supports loading for only one SRAM device.<br>SRAM device core voltage can be any value (was previously limited to 2.5 volts or 3.3 volts).                                                                 | 7.2.1                     |

| ID.  Added list of recommended flash ROM devices.  Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  9.2  was 12.2  table 10.2, 10.3  was 12.2  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | for each function: Function 0/port 1: system vendor ID 72h, system device ID 73h                                                                                                                                      | 8.1                       |

| Updated transmitter termination illustrations.  Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  10.2, 10.3  was 12.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                       | 8.3                       |

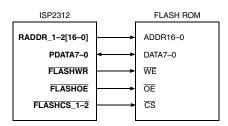

| Removed RISC Clock Frequency Sense Pins section has been removed (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Added list of recommended flash ROM devices.                                                                                                                                                                          | 9.2                       |

| (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the ISP2312 clock frequency).  Changed recommended program to compute differential impedance.  13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Updated transmitter termination illustrations.                                                                                                                                                                        | 10.2, 10.3                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (PDATA3–2 pins are no longer sampled at PCI bus rest to determine the                                                                                                                                                 | was 12.2                  |

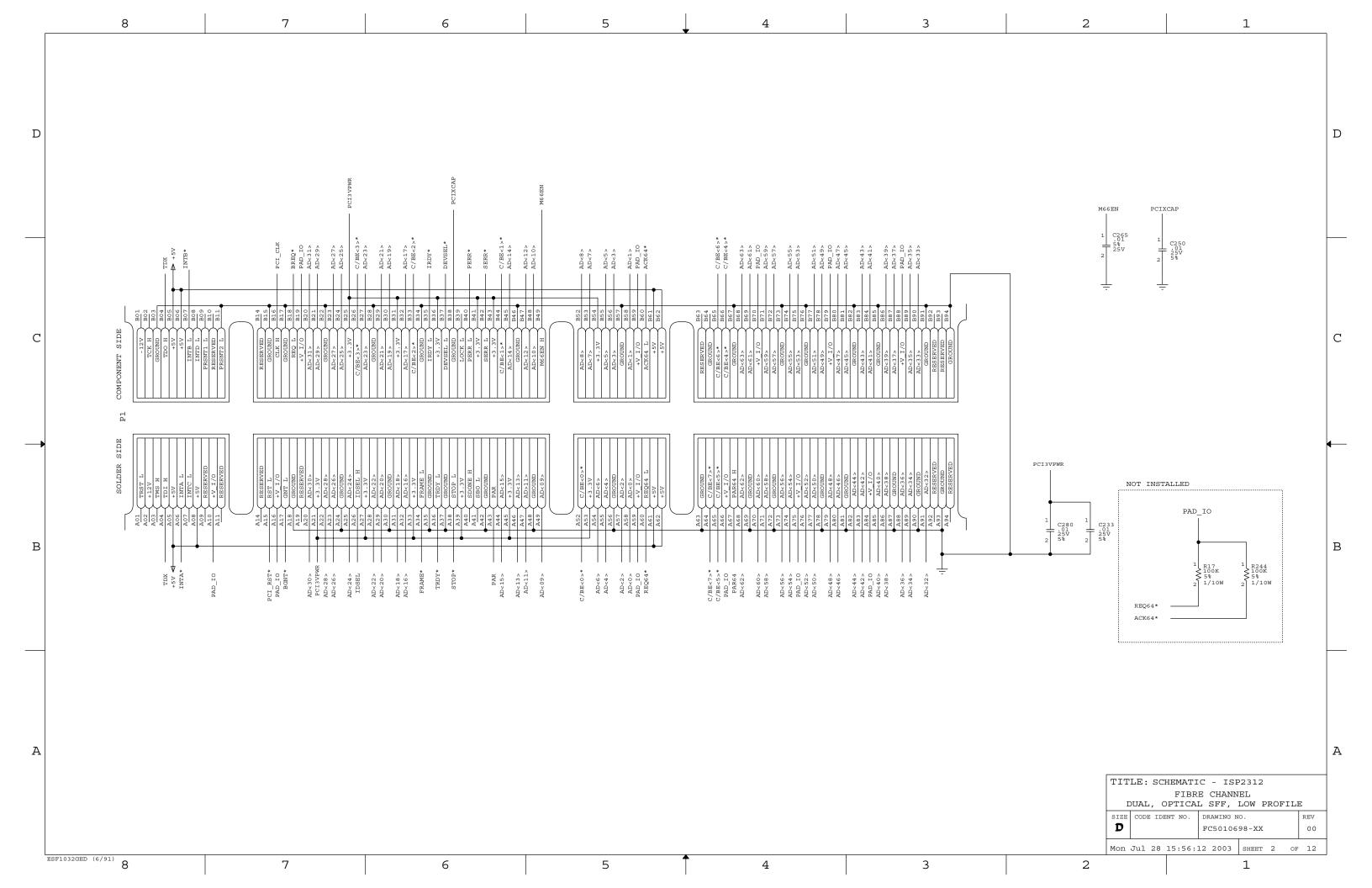

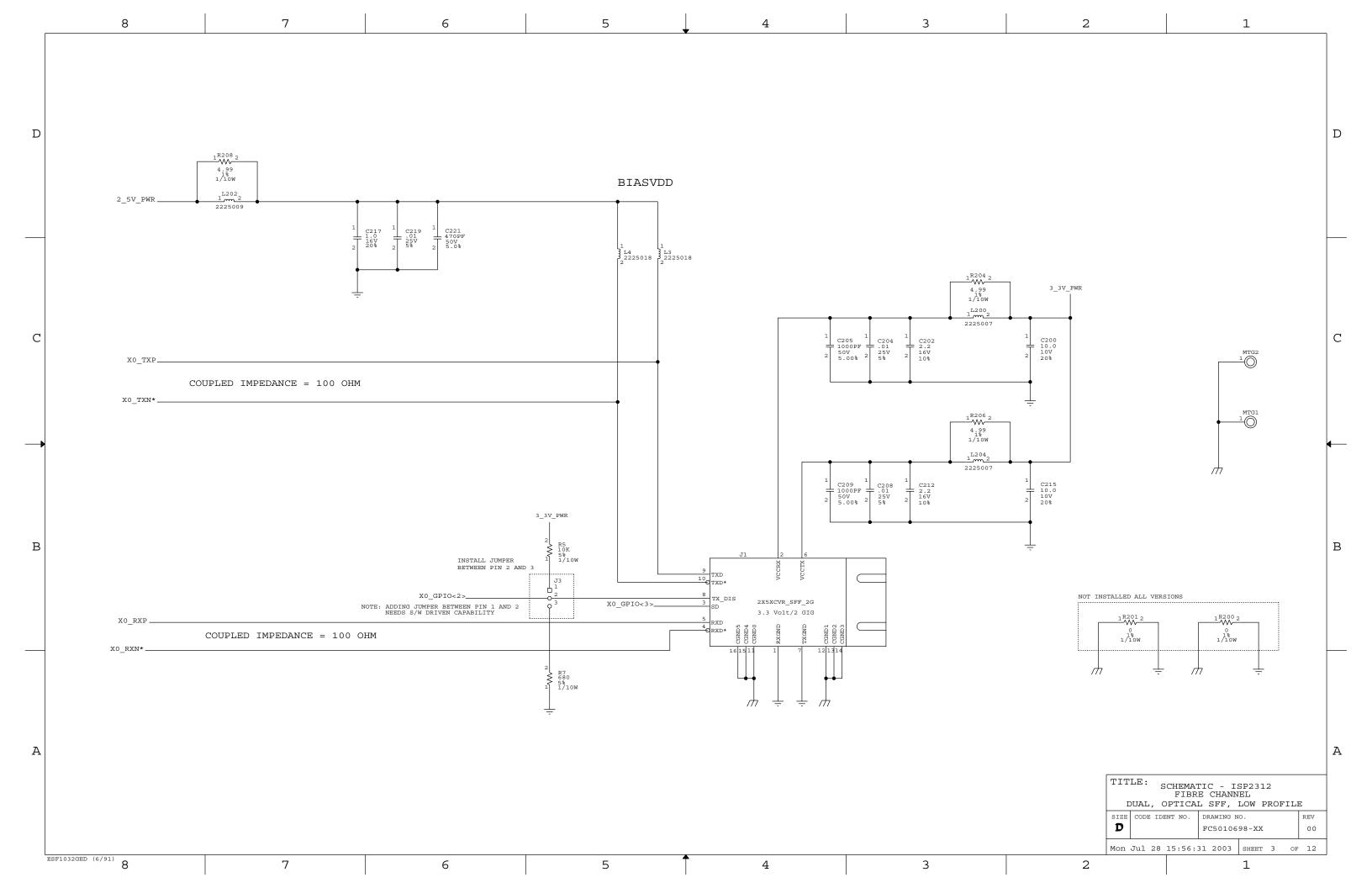

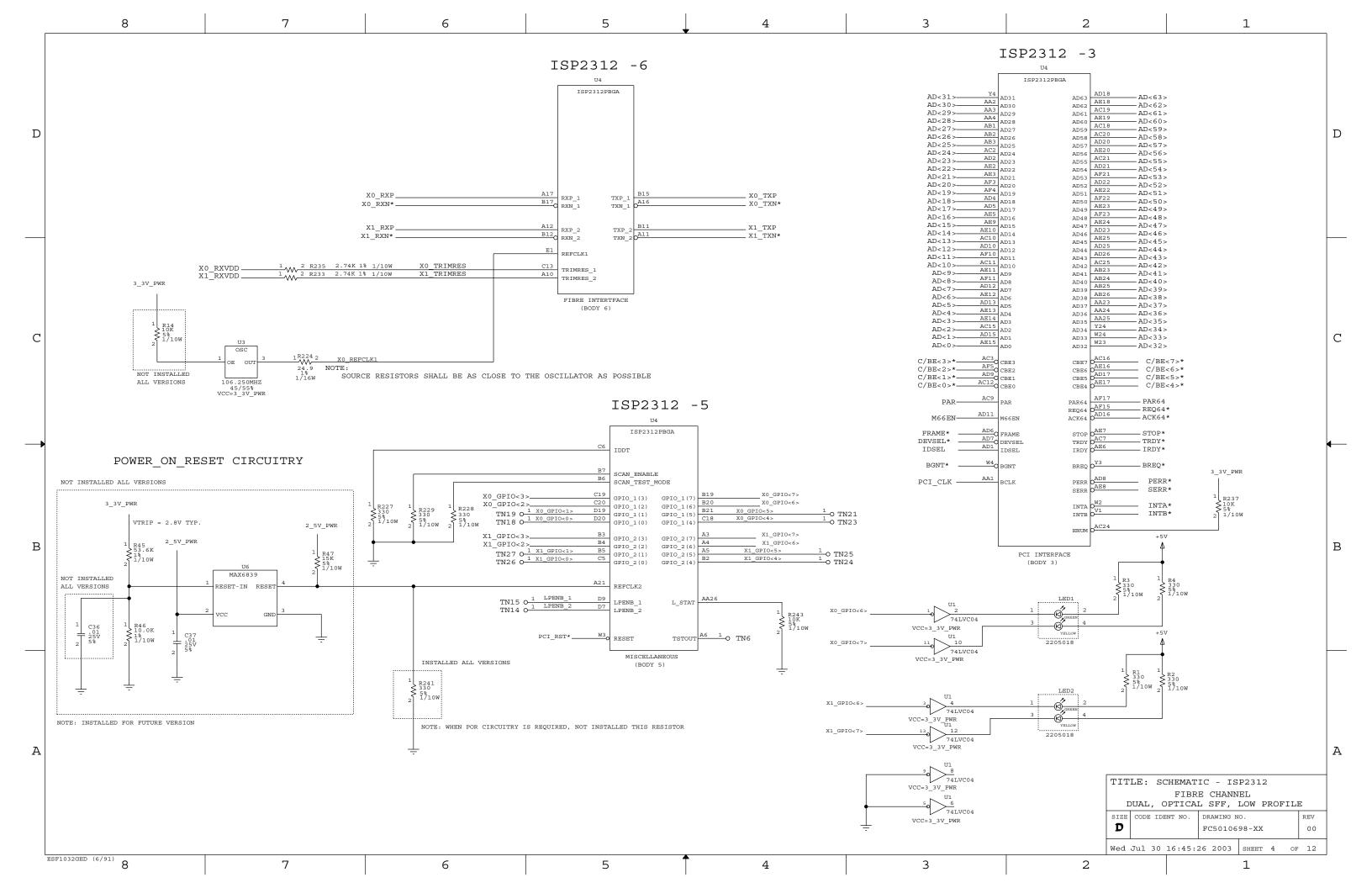

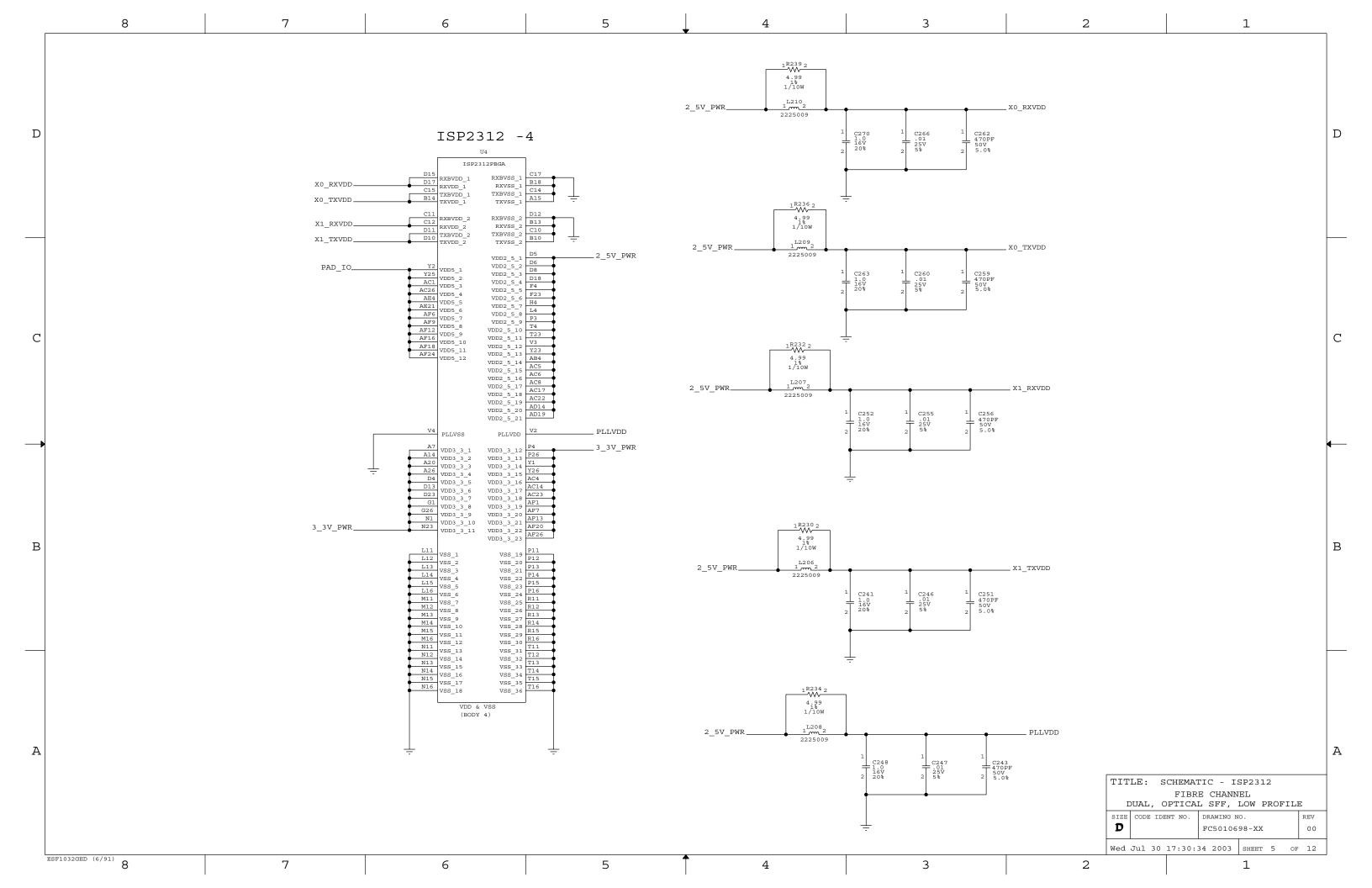

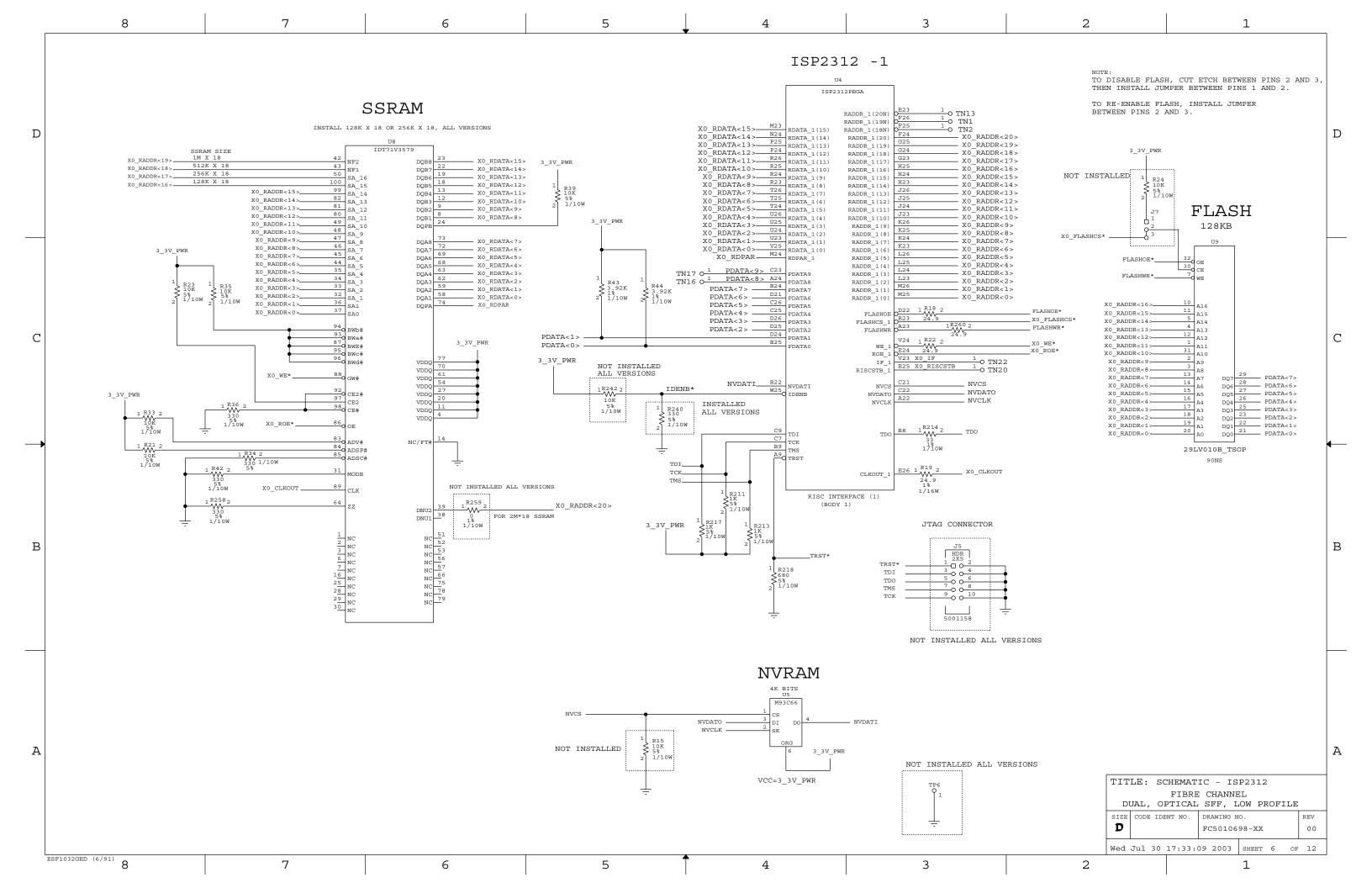

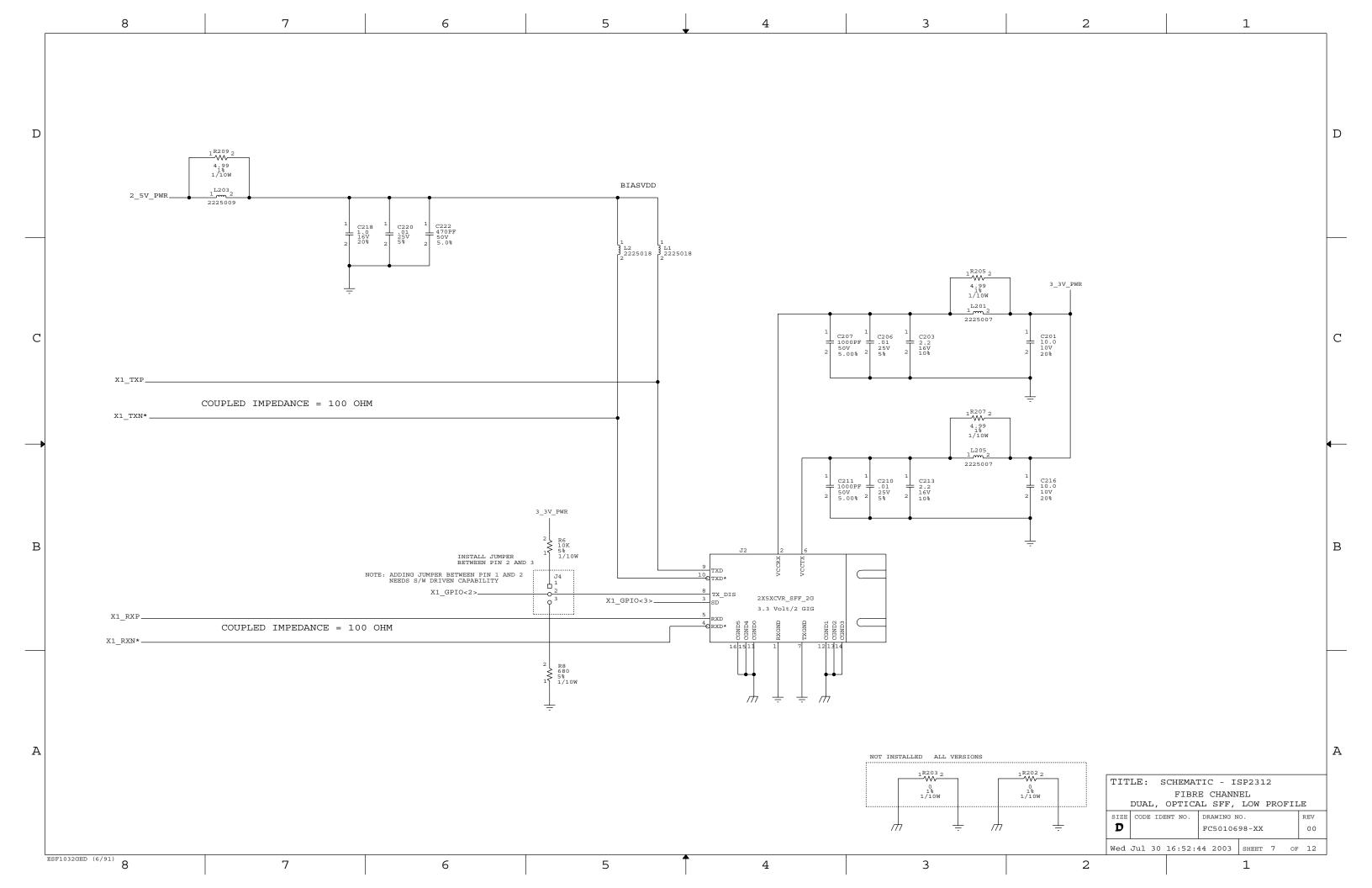

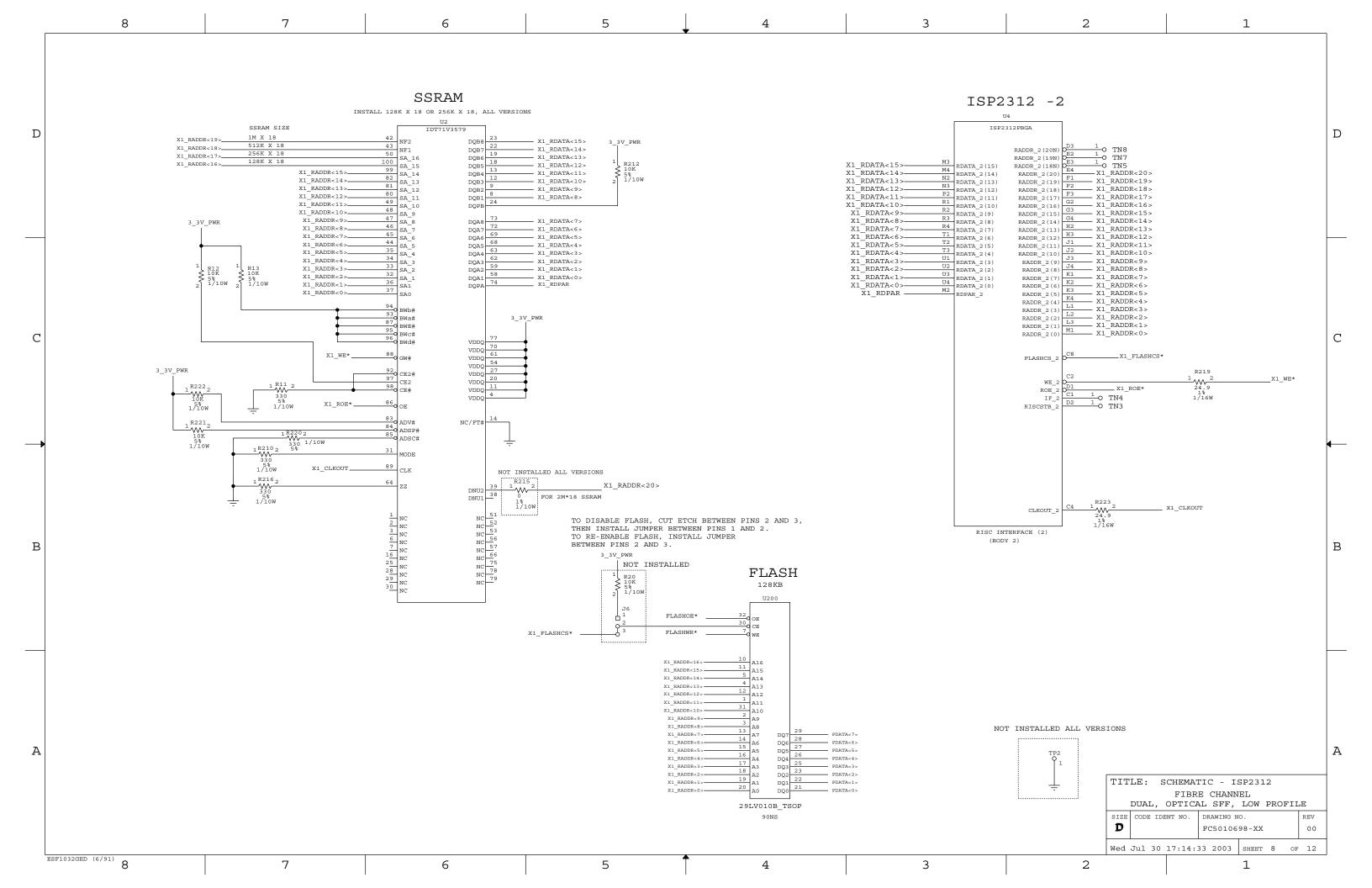

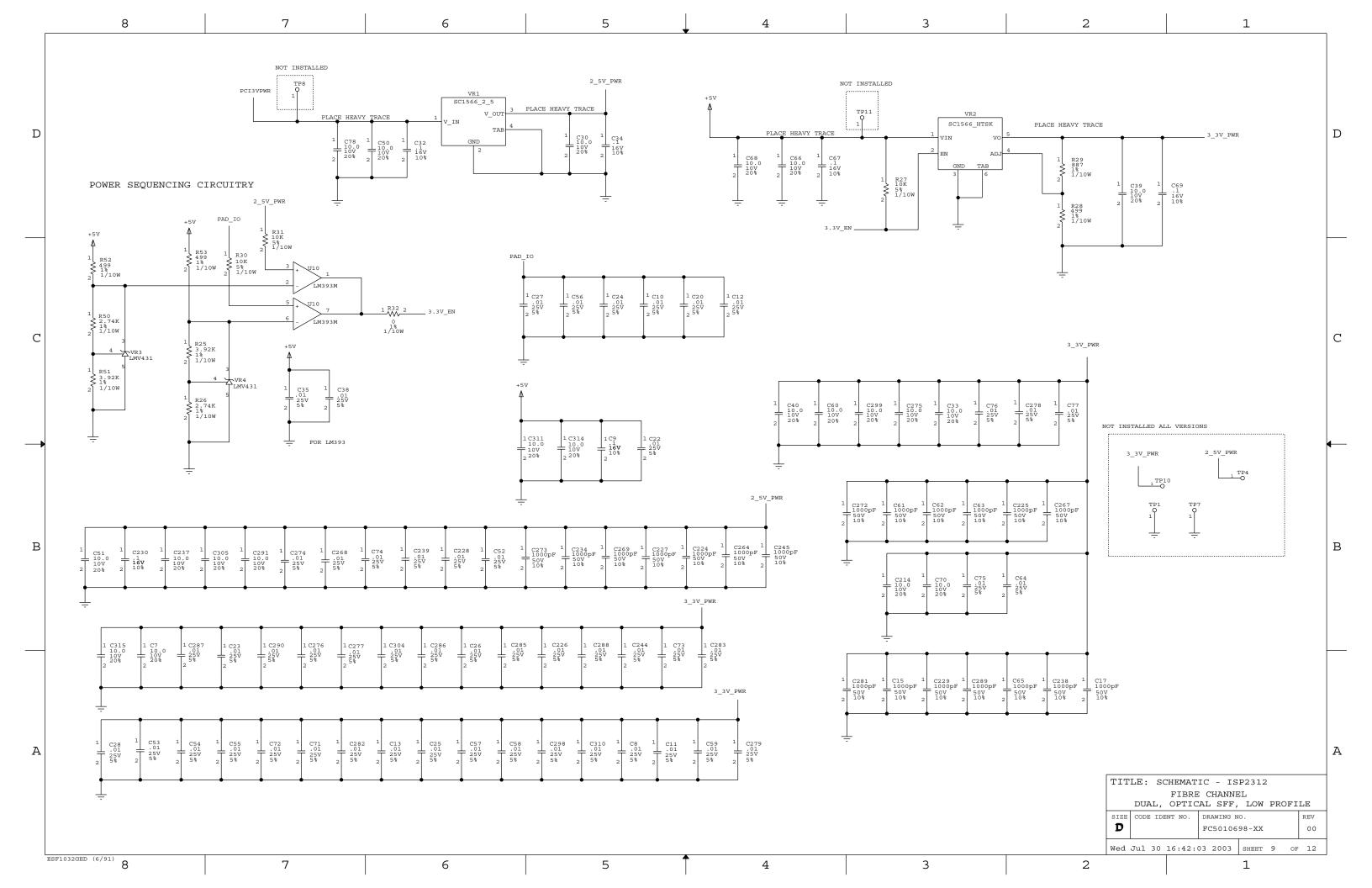

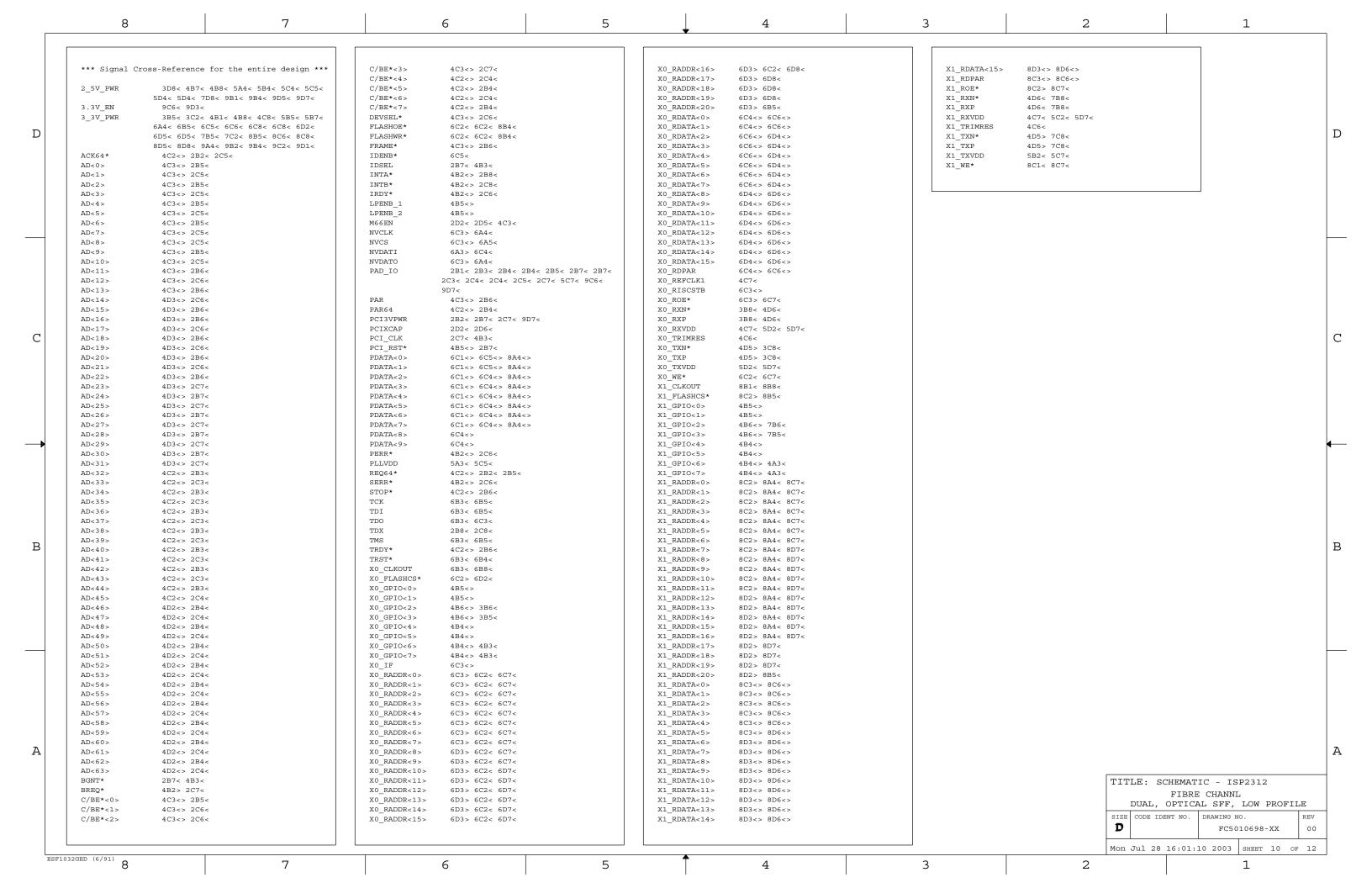

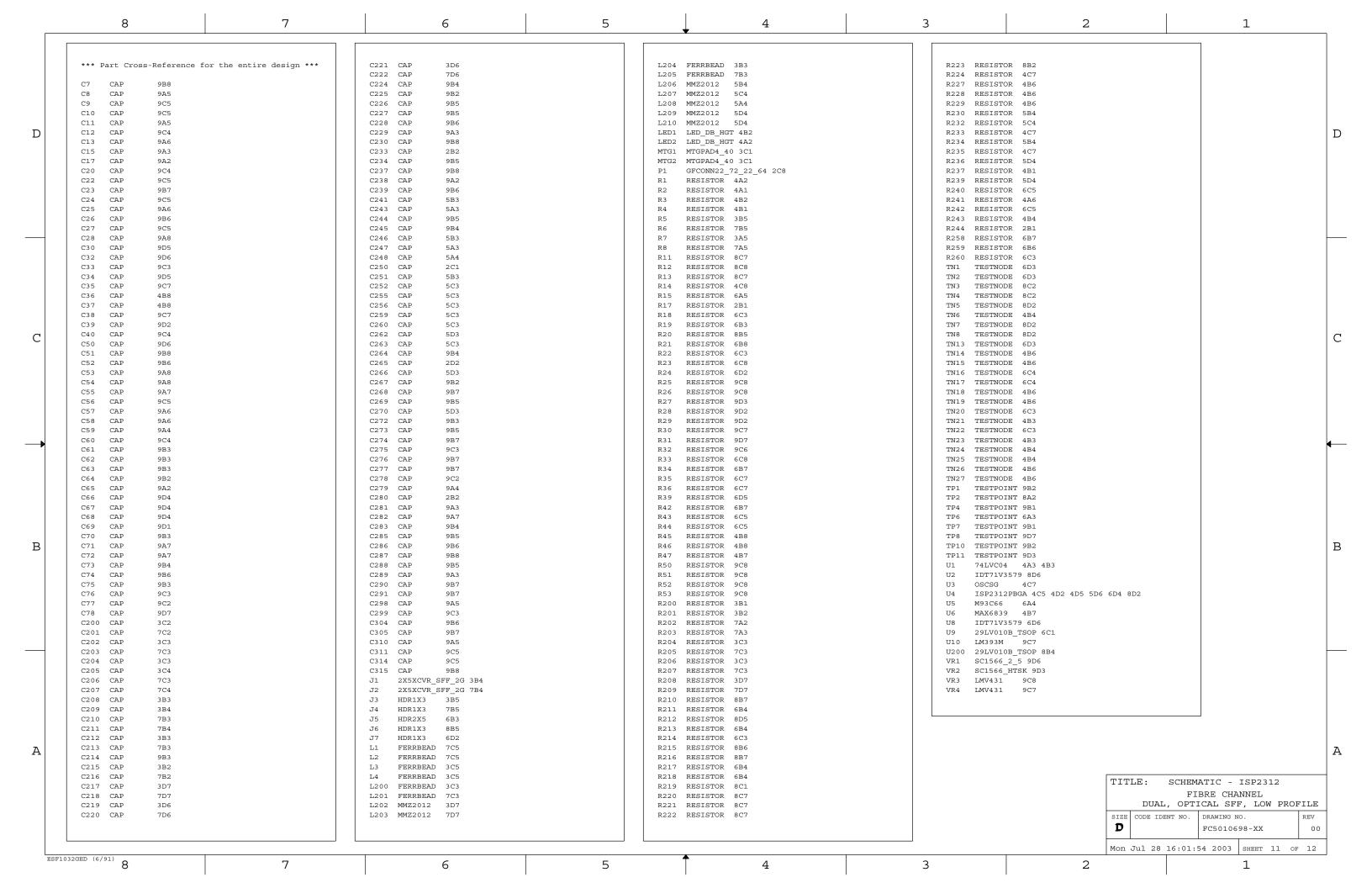

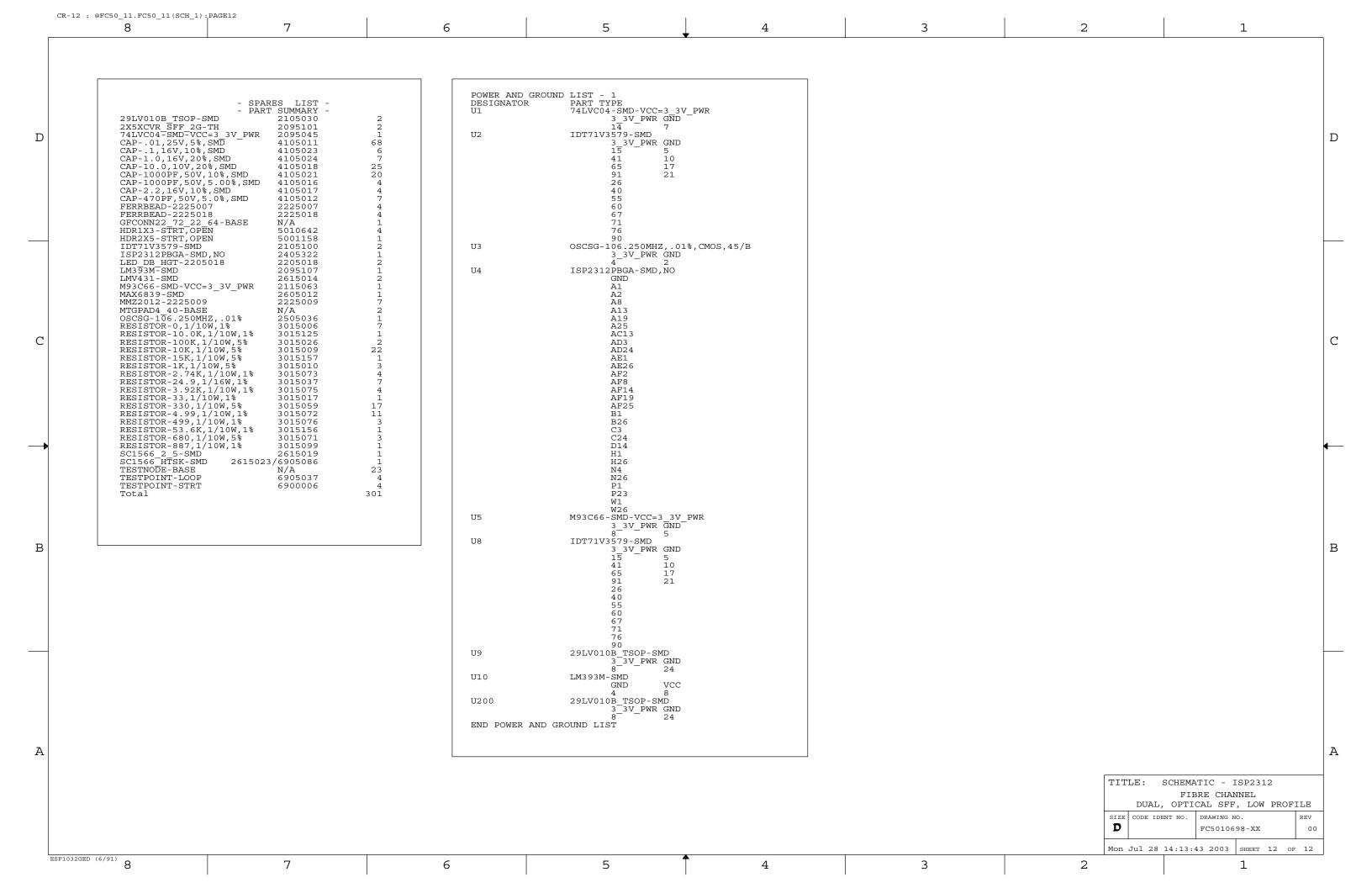

| Updated schematics. 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Changed recommended program to compute differential impedance.                                                                                                                                                        | 13                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Updated schematics.                                                                                                                                                                                                   | 15                        |

83312-508-00 E Page iii

© 2001–2003 QLogic Corporation. All rights reserved worldwide.

First Printed: March 2001

Printed in U.S.A.

QLogic Corporation, 26650 Aliso Viejo Parkway, Aliso Viejo, CA 92656, (800) 662-4471 or (949) 389-6000

Page iv 83312-508-00 E

## **Table of Contents**

| Section 1 | Overview                                         |      |

|-----------|--------------------------------------------------|------|

| 1.1       | Introduction                                     | 1-1  |

| 1.2       | Documentation Conventions                        | 1-2  |

| 1.3       | Features                                         | 1-2  |

| Section 2 | Package Information                              |      |

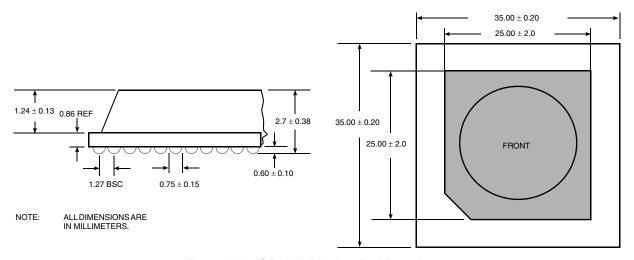

| 2.1       | Mechanical Drawings                              | 2-1  |

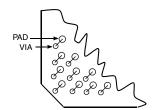

| 2.2       | Pad Stacking                                     | 2-1  |

| 2.3       | Thermal Requirements                             | 2-2  |

| 2.4       | Electrical Characteristics                       | 2-2  |

| Section 3 | Pin Descriptions                                 |      |

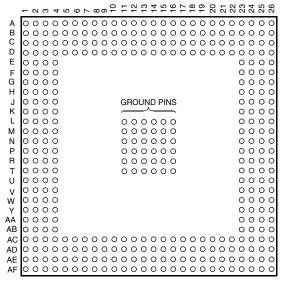

| 3.1       | Pin Configuration                                | 3-1  |

| 3.2       | Pin Descriptions                                 | 3-13 |

| 3.2.1     | Fibre Channel Serial Interfaces 1 and 2 Pins     | 3-14 |

| 3.2.2     | RISC Interfaces 1 and 2 Pins                     | 3-14 |

| 3.2.3     | Flash BIOS 1 and 2 Pins                          | 3-15 |

| 3.2.4     | NVRAM Interface Pins                             | 3-16 |

| 3.2.5     | PCI Bus Interface Pins                           | 3-17 |

| 3.2.6     | JTAG Pins                                        | 3-22 |

| 3.2.7     | Miscellaneous Pins                               | 3-23 |

| 3.2.8     | Power and Ground Pins                            | 3-24 |

| Section 4 | Power Connections                                |      |

| 4.1       | Introduction                                     | 4-1  |

| 4.2       | Compatibility with Future ISP2312 Family Devices | 4-1  |

| 4.3       | Digital Power                                    | 4-1  |

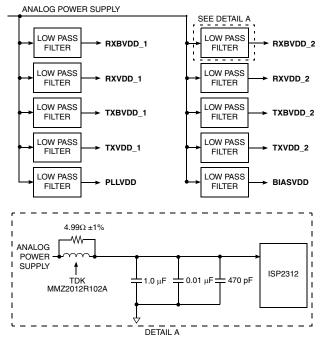

| 4.4       | Analog Power                                     | 4-1  |

| 4.4.1     | Analog Power Input Requirements                  | 4-1  |

| 4.4.2     | Analog Power Input Filtering Requirements        | 4-1  |

| 4.5       | PCI Clamp Voltage Input                          | 4-2  |

| 4.6       | Power Sequencing Recommendations                 | 4-2  |

83312-508-00 E Page v

| Section 5 | Clock Requirements                      |      |

|-----------|-----------------------------------------|------|

| 5.1       | Introduction                            | 5-1  |

| 5.2       | BCLK                                    | 5-1  |

| 5.3       | REFCLK1                                 | 5-2  |

| Section 6 | PCI Interface                           |      |

| 6.1       | Introduction                            | 6-1  |

| 6.2       | Signal Connections                      | 6-1  |

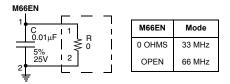

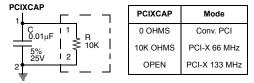

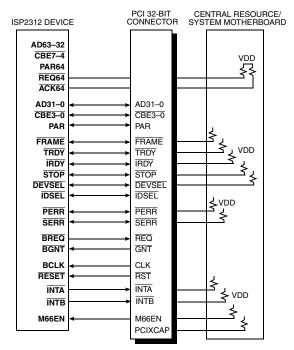

| 6.2.1     | M66EN and PCIXCAP Connections           | 6-1  |

| 6.2.2     | 32-Bit Connections                      | 6-2  |

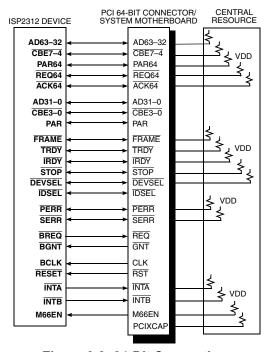

| 6.2.3     | 64-Bit Connections                      | 6-3  |

| 6.3       | PCI Bus Target Mode Operation           | 6-3  |

| 6.3.1     | PCI Bus Address Decode                  | 6-3  |

| 6.3.2     | Target Mode Commands                    | 6-4  |

| 6.4       | Master Mode Commands                    | 6-4  |

| 6.4.1     | Dual Address Cycle                      | 6-5  |

| 6.4.2     | Memory Read                             | 6-5  |

| 6.4.3     | Memory Read Line                        | 6-5  |

| 6.4.4     | Memory Read Multiple                    | 6-6  |

| 6.4.5     | Memory Write                            | 6-6  |

| 6.4.6     | Memory Write and Invalidate             | 6-6  |

| 6.4.7     | Memory Read Block                       | 6-6  |

| 6.4.8     | Memory Write Block                      | 6-6  |

| 6.5       | Data Path and Alignment Logic           | 6-6  |

| 6.6       | PCI Bus Configuration Registers         | 6-8  |

| 6.6.1     | PCI Vendor ID Register                  | 6-10 |

| 6.6.2     | PCI Device ID Register                  | 6-10 |

| 6.6.3     | PCI Command Register                    | 6-10 |

| 6.6.4     | PCI Status Register                     | 6-11 |

| 6.6.5     | PCI Revision ID and Class Code Register | 6-12 |

| 6.6.6     | PCI Cache Line Size Register            | 6-12 |

| 6.6.7     | PCI Latency Timer Register              | 6-13 |

| 6.6.8     | PCI Header Type Register                | 6-13 |

| 6.6.9     | PCI I/O Base Address Register           | 6-14 |

| 6.6.10    | PCI Memory Base Address Registers       | 6-14 |

| 6.6.11    | PCI Subsystem Vendor ID Register        | 6-14 |

| 6.6.12    | PCI Subsystem Device ID Register        | 6-14 |

| 6.6.13    | PCI Expansion ROM Base Address Register | 6-15 |

| 6.6.14    | PCI Capability Pointer Register         | 6-15 |

| 6.6.15    | PCI Interrupt Line Register             | 6-15 |

| 6.6.16    | PCI Interrupt Pin Register              | 6-15 |

| 6.6.17   | PCI Minimum Grant Register                              | 6-16 |

|----------|---------------------------------------------------------|------|

| 6.6.18   | PCI Maximum Latency Register                            | 6-16 |

| 6.6.19   | PCI Power Management Capability Data Structure          | 6-16 |

| 6.6.19.1 | PCI Capability ID Register                              | 6-16 |

| 6.6.19.2 | PCI-X Capability Item Pointer                           | 6-16 |

| 6.6.19.3 | PCI Power Management Capabilities Register              | 6-16 |

| 6.6.19.4 | PCI Power Management Control/Status Register            | 6-17 |

| 6.6.19.5 | PCI Power Management Bridge Support Extensions Register | 6-17 |

| 6.6.19.6 | PCI Power Management Data Register                      | 6-17 |

| 6.6.20   | PCI-X Capability Data Structure                         | 6-17 |

| 6.6.20.1 | PCI-X Capability ID Register                            | 6-17 |

| 6.6.20.2 | PCI MSI Capability Item Pointer Register                | 6-18 |

| 6.6.20.3 | PCI-X Command Register                                  | 6-18 |

| 6.6.20.4 | PCI-X Status Register                                   | 6-19 |

| 6.6.21   | PCI MSI Capability Data Structure                       | 6-20 |

| 6.6.21.1 | PCI MSI Capability ID Register                          | 6-20 |

| 6.6.21.2 | PCI MSI Message Control Register                        | 6-20 |

| 6.6.21.3 | PCI MSI Message Address Register                        | 6-21 |

| 6.6.21.4 | PCI MSI Message Upper Address Register                  | 6-21 |

| 6.6.21.5 | PCI MSI Message Data Register                           | 6-21 |

| 6.6.21.6 | PCI Next Capability Item Pointer Register               | 6-21 |

| 6.6.22   | CompactPCI Hot Swap Capability ID Register              | 6-21 |

| 6.6.23   | CompactPCI Hot Swap Control and Status Register         | 6-22 |

| 6.7      | PCI Bus Interface Registers                             | 6-22 |

| 6.7.1    | Flash BIOS Address Register                             | 6-24 |

| 6.7.2    | Flash BIOS Data Register                                | 6-24 |

| 6.7.3    | ISP Control/Status Register                             | 6-24 |

| 6.7.4    | ISP to PCI Interrupt Control Register                   | 6-26 |

| 6.7.5    | ISP to PCI Interrupt Status Register                    | 6-26 |

| 6.7.6    | ISP Semaphore Register                                  | 6-27 |

| 6.7.7    | ISP Nonvolatile RAM Interface Register                  | 6-27 |

| 6.7.8    | RISC to RISC Semaphore Register                         | 6-28 |

| 6.7.9    | Auto-Request Registers                                  | 6-28 |

| 6.7.9.1  | Request Queue In-Pointer Register                       | 6-28 |

| 6.7.9.2  | Request Queue Out-Pointer Register                      | 6-28 |

| 6.7.9.3  | Response Queue In-Pointer Register                      | 6-28 |

| 6.7.9.4  | Response Queue Out-Pointer Register                     | 6-29 |

| 6.7.10   | RISC to Host Status Low and High Registers              | 6-29 |

| 6.7.11   | Host to Host Semaphore Register                         | 6-29 |

| 6.7.12   | RISC Host Command and Control Register                  | 6-30 |

| 6.7.13   | GPIOD Register                                          | 6-31 |

83312-508-00 E

| 6.7.14<br>6.7.15                             | GPIOE Register                                                                                                                                      | 6-32<br>6-32                                 |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| Section 7                                    | RISC Interface                                                                                                                                      |                                              |

| 7.1<br>7.2<br>7.2.1<br>7.2.2                 | Introduction  RISC Signal Connections  Basic RISC Interface Connections  Debug Connections                                                          | 7-1<br>7-1<br>7-1<br>7-3                     |

| Section 8                                    | NVRAM Interface                                                                                                                                     |                                              |

| 8.1<br>8.2<br>8.3<br>8.4                     | Introduction                                                                                                                                        | 8-1<br>8-1<br>8-2<br>8-2                     |

| Section 9                                    | Flash ROM Interface                                                                                                                                 |                                              |

| 9.1<br>9.2                                   | Introduction                                                                                                                                        | 9-1<br>9-1                                   |

| Section 10                                   | Fibre Channel Interface                                                                                                                             |                                              |

| 10.1<br>10.2<br>10.2.1<br>10.3<br>10.3.1     | Introduction  Fibre Channel Copper Interface Signal Connections  Trim Resistors  Fibre Channel Optical Interface Signal Connections  Trim Resistors | 10-1<br>10-1<br>10-2<br>10-2<br>10-3         |

| Section 11                                   | JTAG Boundary Scan Interface                                                                                                                        |                                              |

| 11.1<br>11.2<br>11.3                         | Introduction                                                                                                                                        | 11-1<br>11-1<br>11-1                         |

| Section 12                                   | Sense Pins                                                                                                                                          |                                              |

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6 | Introduction PCI-X Mode REQ64 Test Modes Subsystem ID Load PCI 2.2 Mode                                                                             | 12-1<br>12-1<br>12-1<br>12-1<br>12-2<br>12-2 |

| Section 13                                   | Layout Considerations                                                                                                                               |                                              |

Page viii 83312-508-00 E

Index

## Section 14 Compatibility with Future ISP2312 Family Devices

### **Section 15 Reference Schematics**

| Section 16  | Timing                                    |            |

|-------------|-------------------------------------------|------------|

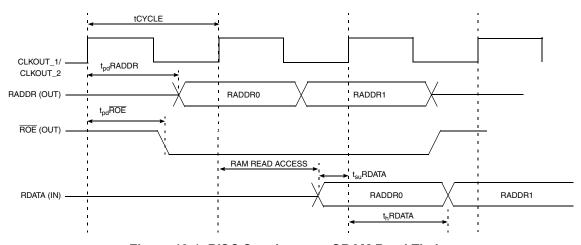

| 16.1        | RISC Processor Timing                     | 16-1       |

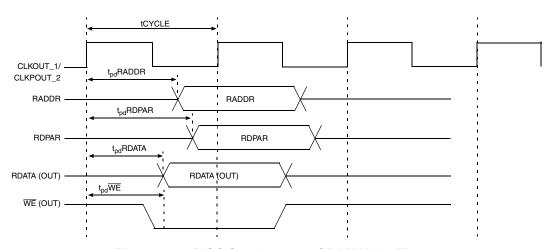

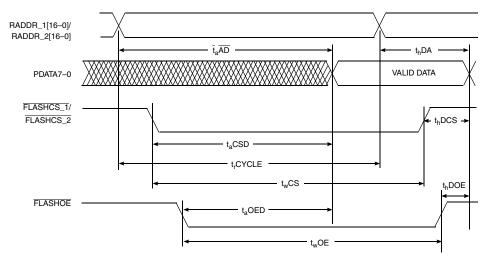

| 16.2        | Flash EPROM Read Timing                   | 16-2       |

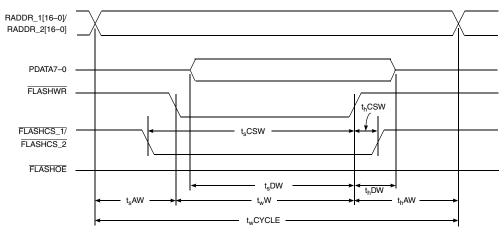

| 16.3        | Flash EPROM Write Timing                  | 16-3       |

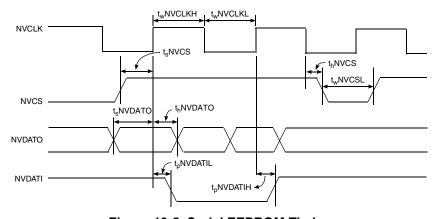

| 16.4        | Serial EEPROM Timing                      | 16-4       |

| Annendiy A  | Danistan Ossana                           |            |

| Appelluix A | Register Summary                          |            |

| A.1         | Register Summary  Register Table Listings | A-1        |

| • •         |                                           | A-1<br>A-5 |

### **FIGURES**

| Figure |                                                       | Page |

|--------|-------------------------------------------------------|------|

| 2-1    | ISP2312 Mechanical Drawings                           | 2-1  |

| 2-2    | PCB Pads and Vias                                     | 2-1  |

| 3-1    | ISP2312 Solder Ball Configuration (Top View)          | 3-1  |

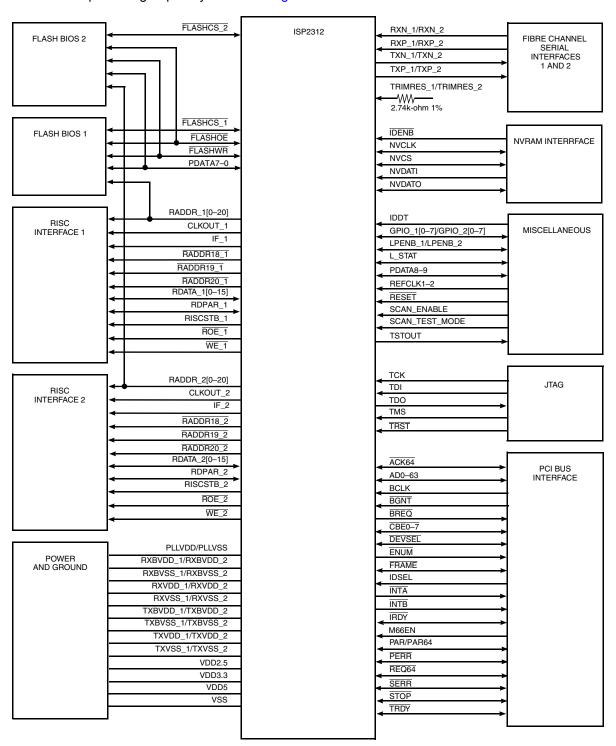

| 3-2    | ISP2312 Functional Signal Grouping                    | 3-2  |

| 4-1    | Analog Power Decoupling                               | 4-2  |

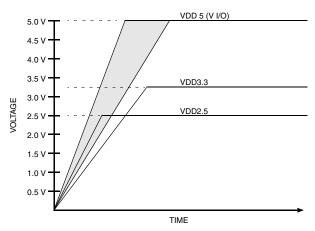

| 4-2    | Power Sequencing—Voltage Versus Time                  | 4-3  |

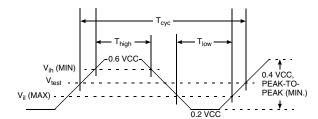

| 5-1    | 3.3-V Clock Waveforms                                 | 5-1  |

| 6-1    | M66EN and PCIXCAP                                     | 6-2  |

| 6-2    | 32-Bit Connections                                    | 6-2  |

| 6-3    | 64-Bit Connections                                    | 6-3  |

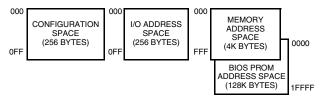

| 6-4    | Target Mode Address Space                             | 6-3  |

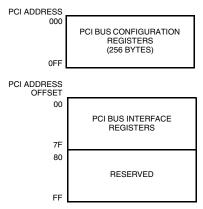

| 6-5    | ISP2312 Register Map                                  | 6-4  |

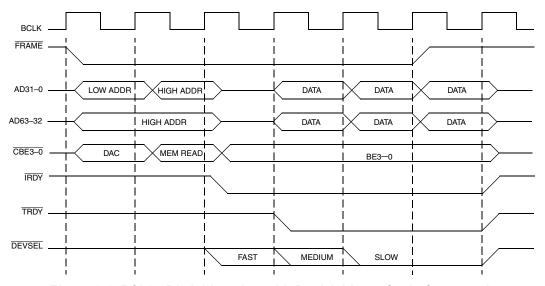

| 6-6    | PCI 64-Bit Addressing with Dual Address Cycle Command | 6-5  |

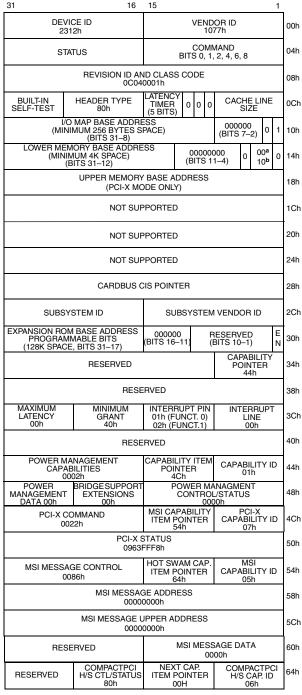

| 6-7    | Configuration Space Header for ISP2312                | 6-13 |

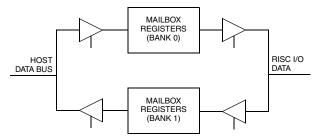

| 6-8    | Mailbox Register Data Paths                           | 6-33 |

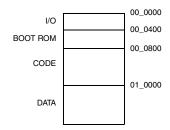

| 7-1    | RISC External SRAM Map                                | 7-1  |

| 7-2    | SRAM Connections                                      | 7-2  |

| 8-1    | ISP2312 NVRAM Connections                             | 8-1  |

| 9-1    | Flash ROM Connection                                  | 9-1  |

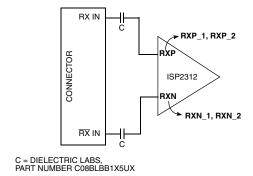

| 10-1   | Receiver Termination (Copper)                         | 10-1 |

|        |                                                       |      |

83312-508-00 E

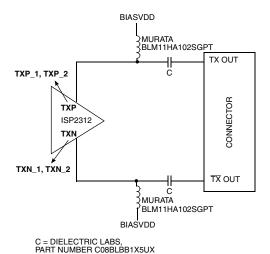

| 10-2 | Transmitter Termination (Copper)   | 10-1 |

|------|------------------------------------|------|

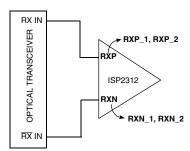

| 10-3 | Receiver Termination (Optical)     | 10-2 |

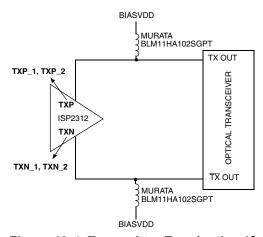

| 10-4 | Transmitter Termination (Optical)  | 10-2 |

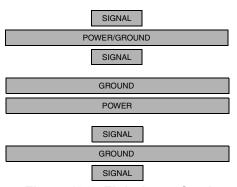

| 13-1 | Eight-Layer Stack                  | 13-1 |

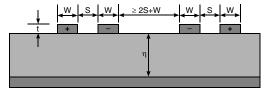

| 13-2 | Coupled Microstrip                 | 13-1 |

| 16-1 | RISC Synchronous SRAM Read Timing  | 16-1 |

| 16-2 | RISC Synchronous SRAM Write Timing | 16-2 |

| 16-3 | Flash EPROM Read Timing            | 16-3 |

| 16-4 | Flash EPROM Write Timing           | 16-4 |

| 16-5 | Serial EEPROM Timing               | 16-4 |

|      |                                    |      |

### **TABLES**

| Table |                                                             | Page |

|-------|-------------------------------------------------------------|------|

| 2-1   | Thermal Parameters                                          | 2-2  |

| 2-2   | Absolute Maximum Stress Ratings                             | 2-2  |

| 2-3   | Operating Conditions                                        | 2-2  |

| 2-4   | DC Characteristics                                          | 2-3  |

| 3-1   | ISP2312 Pins by Location                                    | 3-3  |

| 3-2   | ISP2312 Pins by Name                                        | 3-8  |

| 3-3   | Pin Electrical Characteristics                              | 3-13 |

| 4-1   | Digital Power Pin Input Requirements                        | 4-1  |

| 4-2   | Analog Power Input Requirements                             | 4-1  |

| 5-1   | BCLK AC Specifications                                      | 5-1  |

| 5-2   | REFCLK1 Specifications                                      | 5-2  |

| 6-1   | PCI Interface Pins                                          | 6-1  |

| 6-2   | M66EN and PCIXCAP Connections                               | 6-2  |

| 6-3   | Memory Address Space Target Mode Commands                   | 6-4  |

| 6-4   | Conventional PCI Bus Master Mode Commands                   | 6-4  |

| 6-5   | Starting Address Alignment for PCI 32-Bit Mode Transfers    | 6-7  |

| 6-6   | Starting Address Alignment for PCI 64-Bit Mode Transfers    | 6-7  |

| 6-7   | Data Alignment on the PCI Bus for PCI 32-Bit Mode Transfers | 6-7  |

| 6-8   | Data Alignment on the PCI Bus for PCI 64-Bit Mode Transfers | 6-7  |

| 6-9   | PCI Bus Configuration Registers                             | 6-8  |

| 6-10  | PCI Vendor ID Register                                      | 6-10 |

| 6-11  | PCI Device ID Register                                      | 6-10 |

| 6-12  | PCI Command Register                                        | 6-10 |

| 6-13  | PCI Status Register                                         | 6-11 |

| 6-14  | PCI Revision ID and Class Code Register                     | 6-12 |

| 6-15  | PCI Cache Line Size Register                                | 6-13 |

|       |                                                             |      |

Page x

| 6-16 | PCI Latency Timer Register                               | 6-13 |

|------|----------------------------------------------------------|------|

| 6-17 | PCI Header Type Register                                 | 6-13 |

| 6-18 | PCI I/O Base Address Register                            | 6-14 |

| 6-19 | PCI Lower Memory Base Address Register                   | 6-14 |

| 6-20 | PCI Upper Memory Base Address Register (PCI-X Mode Only) | 6-14 |

| 6-21 | PCI Subsystem Vendor ID Register                         | 6-14 |

| 6-22 | PCI Subsystem Device ID Register                         | 6-15 |

| 6-23 | PCI Expansion ROM Base Address Register                  | 6-15 |

| 6-24 | PCI Capability Pointer Register                          | 6-15 |

| 6-25 | PCI Interrupt Line Register                              | 6-15 |

| 6-26 | PCI Interrupt Pin Register                               | 6-15 |

| 6-27 | PCI Minimum Grant Register                               | 6-16 |

| 6-28 | PCI Maximum Latency Register                             | 6-16 |

| 6-29 | PCI Capability ID Register                               | 6-16 |

| 6-30 | PCI-X Capability Item Pointer Register                   | 6-16 |

| 6-31 | PCI Power Management Capabilities Register               | 6-16 |

| 6-32 | PCI Power Management Control/Status Register             | 6-17 |

| 6-33 | PCI Power Management Bridge Support Extensions Register  | 6-17 |

| 6-34 | PCI Power Management Data Register                       | 6-17 |

| 6-35 | PCI-X Capability ID Register                             | 6-17 |

| 6-36 | PCI MSI Capability Item Pointer Register                 | 6-18 |

| 6-37 | PCI-X Command Register                                   | 6-18 |

| 6-38 | Outstanding Split Transactions                           | 6-18 |

| 6-39 | Maximum Memory Read Byte Count                           | 6-18 |

| 6-40 | PCI-X Status Register                                    | 6-19 |

| 6-41 | PCI MSI Capability ID Register                           | 6-20 |

| 6-42 | PCI MSI Message Control Register                         | 6-20 |

| 6-43 | PCI MSI Message Address Register                         | 6-21 |

| 6-44 | PCI MSI Message Upper Address Register                   | 6-21 |

| 6-45 | PCI MSI Message Data Register                            | 6-21 |

| 6-46 | PCI Next Capability Item Pointer Register                | 6-21 |

| 6-47 | CompactPCI Hot Swap Capability ID Register               | 6-21 |

| 6-48 | CompactPCI Hot Swap Control and Status Register          | 6-22 |

| 6-49 | PCI Bus Interface Registers                              | 6-23 |

| 6-50 | Flash BIOS Address Register                              | 6-24 |

| 6-51 | Flash BIOS Data Register                                 | 6-24 |

| 6-52 | ISP Control/Status Register                              | 6-24 |

| 6-53 | PCI Bus Mode                                             | 6-25 |

| 6-54 | Module Select Field                                      | 6-25 |

| 6-55 | ISP to PCI Interrupt Control Register                    | 6-26 |

| 6-56 | ISP to PCI Interrupt Status Register                     | 6-26 |

| 6-57 | ISP Semaphore Register                                   | 6-27 |

| 6-58 | ISP Nonvolatile RAM Interface Register             | 6-27 |

|------|----------------------------------------------------|------|

| 6-59 | RISC to RISC Semaphore Register                    | 6-28 |

| 6-60 | Request Queue In-Pointer Register                  | 6-28 |

| 6-61 | Request Queue Out-Pointer Register                 | 6-28 |

| 6-62 | Response Queue In-Pointer Register                 | 6-28 |

| 6-63 | Response Queue Out-Pointer Register                | 6-29 |

| 6-64 | RISC to Host Status Low and High Registers         | 6-29 |

| 6-65 | Host to Host Semaphore Register                    | 6-29 |

| 6-66 | Host Command and Control Register                  | 6-30 |

| 6-67 | HCCR Command Field Codes                           | 6-30 |

| 6-68 | Corresponding GPIO Pins and Registers              | 6-31 |

| 6-69 | GPIOD Register                                     | 6-31 |

| 6-70 | GPIOE Register                                     | 6-32 |

| 6-71 | Mailbox Registers                                  | 6-32 |

| 7-1  | RISC Interface Pins                                | 7-1  |

| 7-2  | Recommended SRAM Devices                           | 7-2  |

| 7-3  | RISC Memory Access Decoding                        | 7-3  |

| 8-1  | NVRAM Interface Pins                               | 8-1  |

| 8-2  | Recommended NVRAM Devices                          | 8-2  |

| 8-3  | PCI Subsystem ID and Subsystem Vendor ID Locations | 8-2  |

| 9-1  | Flash ROM Interface Pins                           | 9-1  |

| 9-2  | Recommended Flash ROM Devices                      | 9-1  |

| 10-1 | Serial Interface Pins (Copper)                     | 10-1 |

| 10-2 | Recommended Connector                              | 10-1 |

| 10-3 | Serial Interface Pins (Optical)                    | 10-2 |

| 11-1 | JTAG Interface Pins                                | 11-1 |

| 11-2 | JTAG ID Register                                   | 11-1 |

| 12-1 | PCI Sense Pins                                     | 12-1 |

| 12-2 | Test Modes                                         | 12-1 |

| 16-1 | RISC Synchronous SRAM Read Timing                  | 16-1 |

| 16-2 | RISC Synchronous SRAM Write Timing                 | 16-2 |

| 16-3 | Flash EPROM Read Timing                            | 16-2 |

| 16-4 | Flash EPROM Write Timing                           | 16-3 |

| 16-5 | Serial EPROM Timing                                | 16-4 |

| A-1  | PCI Bus Configuration Registers                    | A-1  |

| A-2  | PCI Bus Interface Registers                        | A-3  |

| A-3  | Mailbox Registers                                  | A-3  |

Page xii 83312-508-00 E

# Section 1 Overview

#### 1.1

#### Introduction

The ISP2312 is a complete PCI to Fibre Channel host adapter on a single chip. This guide is for design engineers who are implementing a board design using the ISP2312 chip. This guide covers all the interfaces of the device and gives details about how to design the ISP2312 into a board-level product. The reader should be familiar with the following PCI and Fibre Channel standards:

- *PCI Local Bus Specification*, revision 2.2, December 8, 1998

- PCI-X Addendum (revision 1.0) to the PCI Local Bus Specification, September 22, 1999

- PCI Bus Power Management Interface Specification revision 1.1 (PC99)

- SCSI-3 Fibre Channel Protocol (SCSI-FCP), X3.269:1996

- Fibre Channel Physical and Signaling Interface (FC-PH) X3.230:1994

- Fibre Channel 2nd Generation (FC-PH-2), X3.297:1997

- Third Generation Fibre Channel Physical and Signaling Interface (FC-PH-3), X3.303:1998

- Fibre Channel—Arbitrated Loop (FC-AL-2), working draft, revision 6.4, August 28, 1998

- Fibre Channel Fabric Loop Attachment Technical Report (FC-FLA) NCITS/TR-20:1998

- Fibre Channel—Private Loop Direct Attach Technical Report (FC-PLDA), NCITS/TR-19:1998

- Fibre Channel Tape (FC-TAPE) profile, T11/99-069v4, revision 1.17, May 14, 1999

- SCSI Fibre Channel Protocol-2 (FCP-2) working draft, revision 3, October 1, 1999

- ANSI Information Technology—SCSI 3

Architecture Model, revision 18, November 27, 1995

Note that this document does not cover firmware or software.

Topics covered in each section are summarized below.

- Section 1—Overview. This section describes the content of this guide and its audience.

- Section 2—Package Information. This section contains information about the ISP2312 chip.

- Section 3—Pin Descriptions. This section defines the pins on the ISP2312 chip.

- Section 4—Power Connections. This section defines the digital and analog power requirements and PCI clamp voltage input for the ISP2312 chip.

- Section 5—Clock Requirements. This section defines the requirements for the BCLK and REFCLK1 clock inputs for the ISP2312 chip.

- Section 6—PCI Interface. This section defines the PCI connections to the ISP2312 chip.

- Section 7—RISC Interface. This section defines the RISC interface connections to the ISP2312 chip.

- Section 8—NVRAM Interface. This section defines the NVRAM interface connections to the ISP2312 chip.

- Section 9—Flash ROM Interface. This section defines the Flash ROM interface connections to the ISP2312 chip.

- **NOTE:** The flash BIOS pins can be used only during the power-up initialization sequence. When the ISP2312 begins normal operations, some flash BIOS pins become RISC interface pins.

- Section 10—Fibre Channel Interface. This section defines the Fibre Channel interface connections to the ISP2312 chip.

83312-508-00 E 1–1

- Section 11—JTAG Boundary Scan Interface. This section defines the JTAG boundary scan interface connections to the ISP2312 chip.

- Section 12—Sense Pins. This section what pins the ISP2312 samples at power up to determine certain settings, such as the chip operating mode, RISC clock frequency, and PCI-X mode.

- Section 13—Layout Considerations. This section contains recommendations to consider when designing the printed circuit board (PCB).

- Section 14—Compatibility with Future ISP2312 Devices. This section summarizes the PCB design changes necessary to accommodate future ISP2312 devices.

- Section 15—Reference Schematics. This section defines the ISP2312 chip reference schematics.

- **Section 16—Timing.** This section contains RISC and EEPROM timing diagrams.

- Appendix A—Register Summary. This section lists the PCI registers described in this quide.

- Index. The index lists major subjects and concepts with page numbers for easy reference.

## 1.2 Documentation Conventions

The *ISP2312 Designer's Guide* uses the following documentation conventions:

In graphics, ISP2312 pins are always bold, as illustrated below.

- Information that is very important to the board design is set off by **bold** text.

- Information that is critical to the board design is set off by a note:

**NOTE:** Be sure to read everything in the note boxes.

## 1.3 Features

The following features are available in the ISP2312:

- Two completely independent 2-Gb serial Fibre Channel ports, each identical in functionality to the single Fibre Channel port on the ISP2300/2310

- Support for multifunction PCI

- Two of each of the following modules to support the two Fibre Channel ports:

- □ Internal RISC processor

- □ Receive DMA sequencer

- Frame buffer

- DMA channels (transmit, receive, command, auto-request, and auto-response)

- Support for JTAG boundary scan for I/Os; full scan for internal logic and built-in self test (BIST) for onboard memories

- Support for CompactPCI Hot Swap (PCI 2.2 mode only)

- PCI-X support

- Support for Fibre Channel virtual interface (VI) protocol

- Support for 2-Gb Fibre Channel using internal or external transceivers

- Automatically negotiates Fibre Channel bit rate (1 Gb or 2 Gb)

- Supports up to 400 MBps sustained Fibre Channel data transfer rate

- Complete data and code parity protection

- No host intervention required to execute complete SCSI, IP, or VI operations

- Supports multi-ID aliasing in target mode

- Improved loopback functionally

1–2 83312-508-00 E

# Section 2 Package Information

## 2.1 **Mechanical Drawings**

The ISP2312 is packaged in a 388-pin thermally enhanced package plastic ball grid array (EPBGA-T). The ISP2312 mechanical drawings are illustrated in figure 2-1.

Figure 2-1. ISP2312 Mechanical Drawings

## 2.2 Pad Stacking

Adhere to the following requirements when creating the printed circuit board (PCB) pads to place the ISP2312 on the PCB.

- Determine the placement and spacing of the pads from the mechanical drawing (see figure 2-1).

- The PCB pads must be 0.026-inch in diameter.

- The PCB pad solder mask must be a 0.026-inch diameter hole.

- Each PCB pad must have a via. Place each via diagonally from its pad, equidistant from the surrounding pads. The via pad must be 0.020-inch in diameter and have a central 0.010-inch diameter finish hole. Cover the vias with the solder mask. Connect the vias to their pad with a maximum width etch of 0.007 inch for signals, 0.10 for power and ground.

■ Use a 0.026-inch pad with a 0.030-inch ball to allow for a 0.015–0.018-inch collapse of the ball during solder reflow (see figure 2-2).

Figure 2-2. PCB Pads and Vias

83312-508-00 E 2–1

## 2.3 Thermal Requirements

Proper cooling must be provided in all applications so that the maximum operating temperature of the ISP2312 remains within the specified limits. The thermal information for the ISP2312 is listed in table 2-1.

## 2.4 Electrical Characteristics

Tables 2-2 through 2-4 define the ISP2312 electrical characteristics.

Table 2-1. Thermal Parameters

| Name | Description                            | Value        |

|------|----------------------------------------|--------------|

| Pmax | Maximum power dissipation              | 3.975 watts  |

| Tc   | Maximum case temperature  @ Pmax       | 87.7°C       |

| Tj   | Maximum junction temperature @ Pmax    | 100°C        |

| θја  | Junction to ambient thermal impedance: |              |

|      | No airflow                             | 12.4°C/watts |

|      | 0.5 meter/sec airflow                  | 10.7°C/watts |

|      | 1.0 meter/sec airflow                  | 9.9°C/watts  |

|      | 2.0 meters/sec airflow                 | 9.1°C/watts  |

|      | 3.0 meters/sec airflow                 | 8.6°C/watts  |

| θјс  | Junction to case thermal impedance     | 3.1°C/watts  |

Table Notes

Do not exceed the maximum case or junction temperature limits in this table while power is applied.

Table 2-2. Absolute Maximum Stress Ratings

| Symbol | Description                                    | Rating                                             | Unit        |

|--------|------------------------------------------------|----------------------------------------------------|-------------|

| TSTG   | Storage temperature                            | -40 to 125                                         | °C          |

| VDD2.5 | Supply voltage                                 | -0.3 to 3.1                                        | V           |