# Aspect Architecture Document

Pikes Peak hardware platform

Document: 45555-00

Preliminary Revision: P:A.4:A.3:A.4:A.3:A.3:A.1:A.3:A.1:A.4

Revision Date: 3/22/2010

---

This document and information herein is the property of LSI Corp.

All unauthorized use and reproduction is prohibited.

Copyright © 2010, LSI Corp. All rights reserved.

## TABLE OF CONTENTS

|                                                                             |           |

|-----------------------------------------------------------------------------|-----------|

| <b>Table of Contents.....</b>                                               | <b>1</b>  |

| <b>List of Figures.....</b>                                                 | <b>6</b>  |

| <b>List of Tables.....</b>                                                  | <b>7</b>  |

| <b>Source Document Information.....</b>                                     | <b>8</b>  |

| <b>1. Pikes Peak hardware platform - An Overview.....</b>                   | <b>12</b> |

| 1.1. Aspect Introduction.....                                               | 12        |

| 1.1.1. Aspect Description.....                                              | 12        |

| 1.1.2. Assumptions.....                                                     | 14        |

| 1.1.3. Related Documents.....                                               | 14        |

| 1.1.4. Open Issues.....                                                     | 15        |

| 1.1.5. AAD References.....                                                  | 16        |

| 1.2. Aspect High Level Requirements.....                                    | 16        |

| 1.2.1. Product Requirements.....                                            | 16        |

| 1.2.2. AAD Overview.....                                                    | 17        |

| <b>2. Pikes Peak Controller - Element Requirements.....</b>                 | <b>18</b> |

| 2.1. Pikes Peak hardware platform - Element Requirements.....               | 18        |

| 2.1.1. Introduction.....                                                    | 18        |

| 2.1.2. Operational Behavior.....                                            | 18        |

| 2.1.2.1. Host Interface Characteristics.....                                | 18        |

| 2.1.2.2. Drive Interface Characteristics.....                               | 18        |

| 2.1.2.3. General Controller Characteristics.....                            | 19        |

| 2.1.2.4. Controller Identifiers.....                                        | 21        |

| 2.1.2.5. Battery Management.....                                            | 21        |

| 2.1.2.6. Smart Battery Parameters.....                                      | 22        |

| 2.1.2.7. Seven Segment Display Support.....                                 | 23        |

| 2.1.2.8. Protection Information Capability.....                             | 23        |

| 2.1.2.9. Field Replaceable Cache Memory.....                                | 24        |

| 2.1.2.10. Field Replaceable Cache Backup Device.....                        | 24        |

| 2.1.2.11. Field Replaceable HICs.....                                       | 24        |

| 2.1.2.12. Push Button Support.....                                          | 25        |

| 2.1.2.13. USB Port.....                                                     | 25        |

| 2.1.2.14. miniUSB Port.....                                                 | 25        |

| 2.1.2.15. Power Supply.....                                                 | 25        |

| 2.1.2.16. Wake on LAN Support (WOL).....                                    | 26        |

| 2.2. Controller Type Mismatch - Element Requirements.....                   | 26        |

| 2.2.1. Introduction.....                                                    | 26        |

| 2.2.2. Operational Behavior.....                                            | 26        |

| 2.2.2.1. Controller Hot-Swapped with Incorrect Controller Type.....         | 26        |

| 2.2.2.2. Controller Hot-Swapped with same Controller Type.....              | 26        |

| 2.2.2.3. Controller A or B Cold-Swapped with Incorrect Controller Type..... | 26        |

| 2.2.2.4. Power Cycle after Hot-Swap with Incorrect Controller Type.....     | 27        |

| 2.2.2.5. Controller-Drive Enclosure Considerations.....                     | 27        |

| 2.2.2.6. Dual Controller Swap.....                                          | 27        |

|                                                                     |           |

|---------------------------------------------------------------------|-----------|

| 2.2.2.7. Start-of-Day Mismatch Detection.....                       | 27        |

| 2.2.2.8. Run-Time Mismatch Detection.....                           | 28        |

| 2.2.2.9. Failure to Determine Alternate Board Identifier.....       | 28        |

| 2.2.3. Administrative and Configuration Interfaces.....             | 28        |

| 2.2.3.1. Controller Mismatch Reporting.....                         | 28        |

| 2.2.4. Error Handling and Event Notification.....                   | 28        |

| 2.2.4.1. Controller Type Mismatch.....                              | 28        |

| 2.2.4.2. Device Reported Events.....                                | 28        |

| 2.3. Host Interface Cards - Element Requirements.....               | 29        |

| 2.3.1. Introduction.....                                            | 29        |

| 2.3.2. Operational Behavior.....                                    | 29        |

| 2.3.2.1. Fibre Channel Host Interface Card (Manitou).....           | 29        |

| 2.3.2.2. InfiniBand Host Interface Card (Elk Park).....             | 29        |

| 2.3.2.3. iSCSI-SFP+ Host Interface Card (Glen Cove).....            | 29        |

| 2.4. SATA Flash Disk Support - Element Requirements.....            | 30        |

| 2.4.1. Introduction.....                                            | 30        |

| 2.4.2. Operational Behavior.....                                    | 30        |

| 2.4.2.1. Partitioning.....                                          | 30        |

| 2.4.2.2. Default boot partition.....                                | 31        |

| 2.4.2.3. Mirroring.....                                             | 31        |

| 2.4.2.4. Disk Configuration Information.....                        | 31        |

| 2.4.2.5. Disk Management and Replacement.....                       | 31        |

| 2.4.2.6. SATA flash disk configurations.....                        | 31        |

| 2.4.3. Administrative and Configuration Interfaces.....             | 32        |

| 2.4.3.1. Management Interface.....                                  | 32        |

| 2.4.4. Error Handling and Event Notification.....                   | 32        |

| 2.4.4.1. Invalid SATA flash disk configurations.....                | 32        |

| 2.5. Auto MDIX - Element Requirements.....                          | 32        |

| 2.5.1. Element Functional Behavior Changes.....                     | 32        |

| 2.5.2. Introduction.....                                            | 32        |

| 2.5.3. Operational Behavior.....                                    | 33        |

| 2.5.3.1. Ethernet Ports.....                                        | 33        |

| 2.6. ECC and PCI Error Handling - Element Requirements.....         | 33        |

| 2.6.1. Introduction.....                                            | 33        |

| 2.6.2. Operational Behavior.....                                    | 33        |

| 2.6.2.1. ECC Error Detection and Recovery.....                      | 33        |

| 2.6.2.2. Patrol Scrub.....                                          | 33        |

| 2.6.2.3. PCI/PCIe Error Detection and Recovery.....                 | 34        |

| 2.6.3. Error Handling and Event Notification.....                   | 34        |

| 2.6.3.1. ECC Error.....                                             | 34        |

| 2.6.3.2. PCI/PCIe Error.....                                        | 34        |

| 2.7. Wake on LAN Support - Element Requirements.....                | 34        |

| 2.7.1. Introduction.....                                            | 34        |

| <b>3. Pikes Peak hardware platform - Detailed Architecture.....</b> | <b>35</b> |

| 3.1. Pikes Peak hardware platform - Detailed Architecture.....      | 35        |

| 3.1.1. High Level Design.....                                       | 35        |

|                                                                                                                  |    |

|------------------------------------------------------------------------------------------------------------------|----|

| 3.1.1.1. Details.....                                                                                            | 35 |

| 3.1.1.1.1. Local Controller Baseboard ID.....                                                                    | 35 |

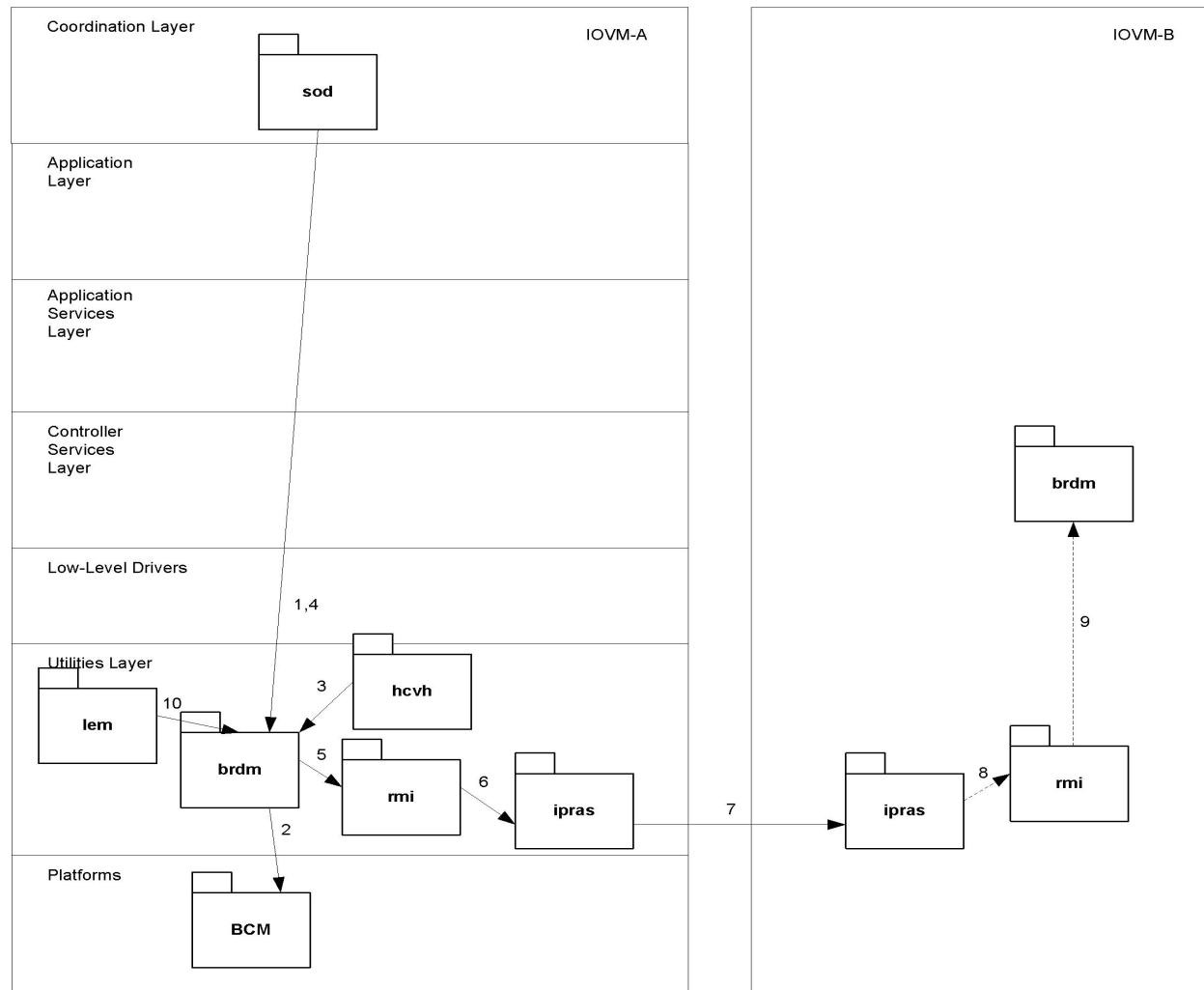

| 3.1.1.1.2. Alternate Controller Baseboard ID.....                                                                | 35 |

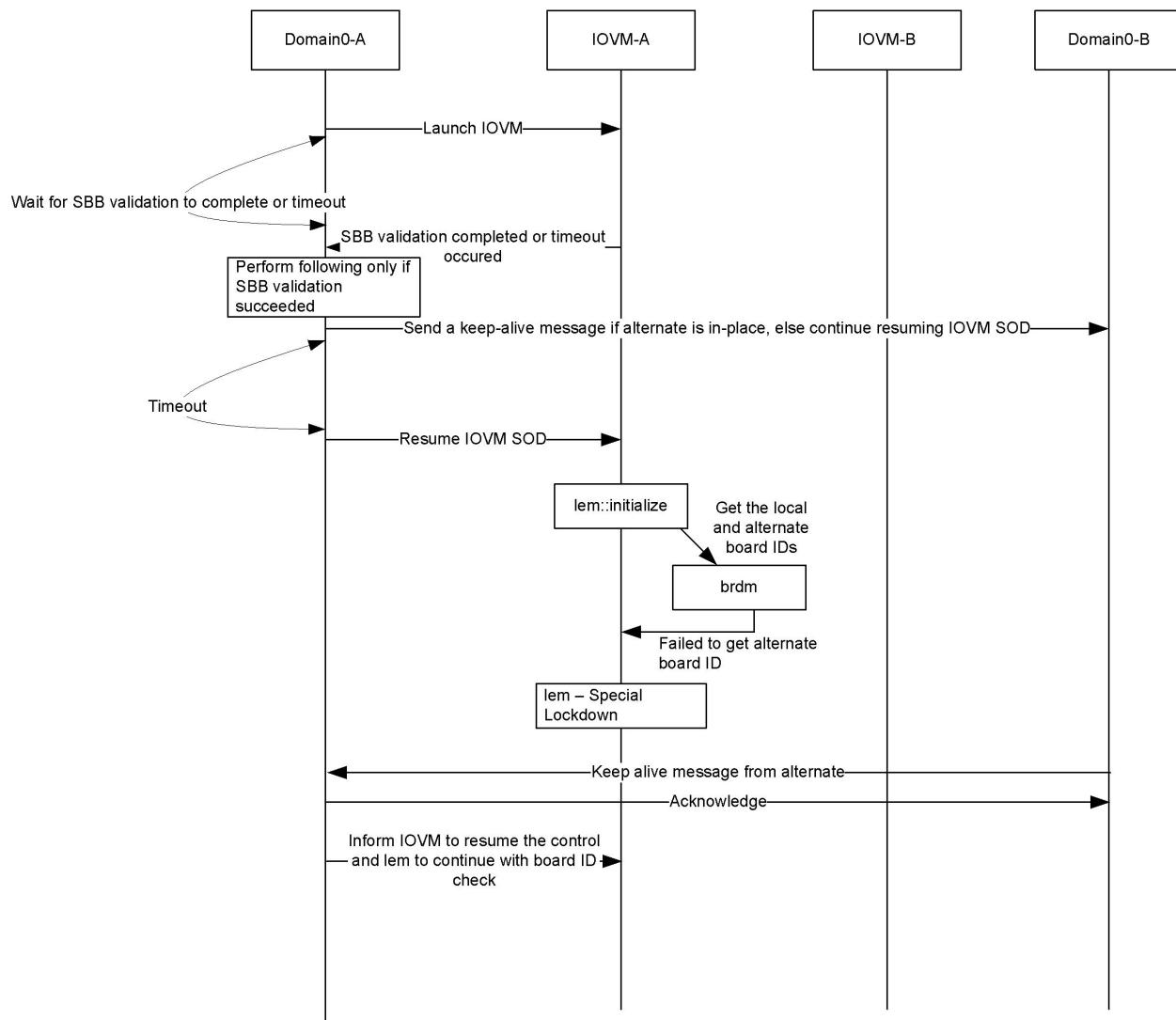

| 3.1.1.1.2.1. Error getting alternate controller's constructed baseboard ID.....                                  | 37 |

| 3.1.1.1.3. Host Board ID.....                                                                                    | 37 |

| 3.1.1.1.4. SBB Validation.....                                                                                   | 37 |

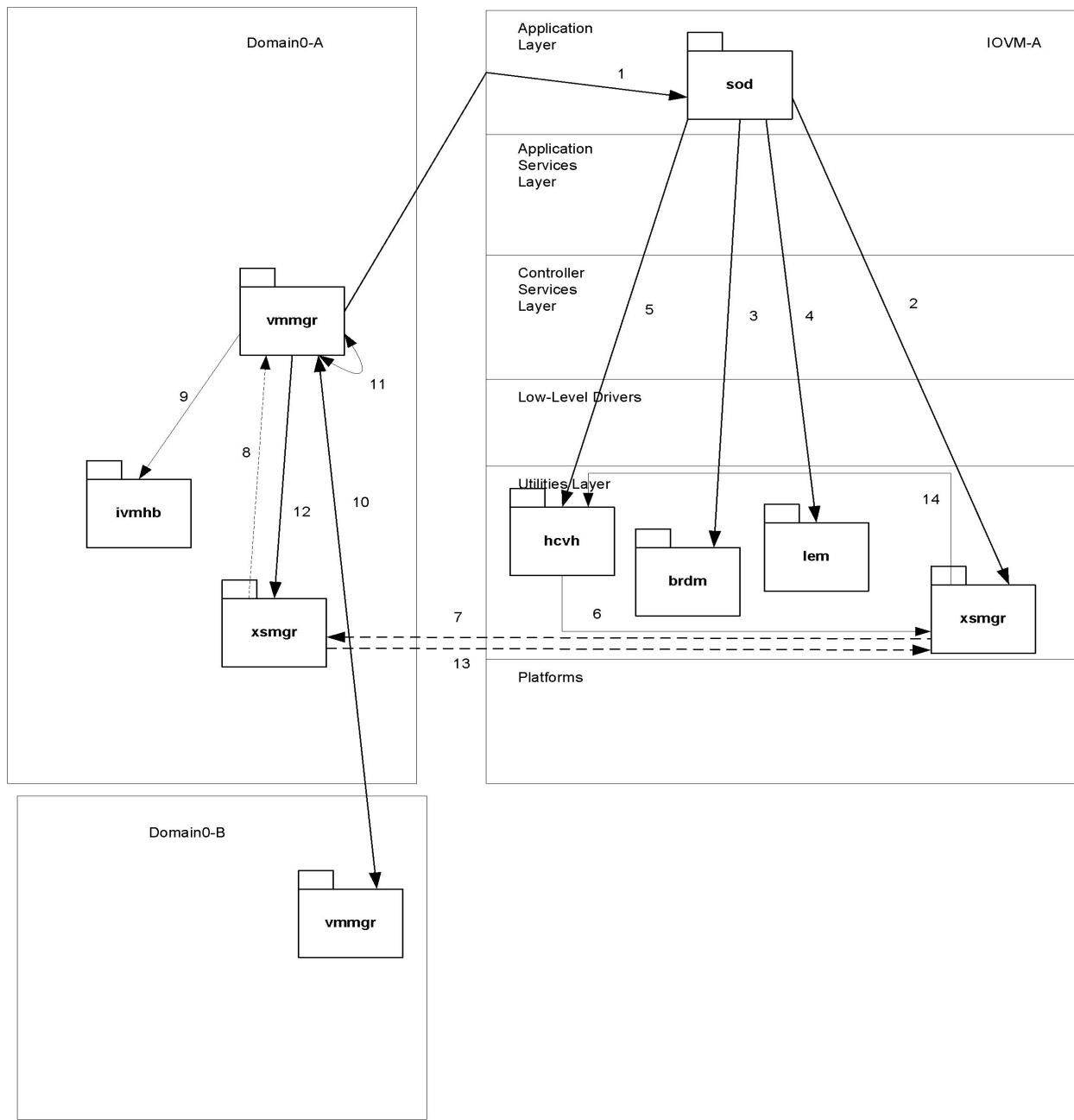

| 3.1.1.1.4.1. SBB Validation Success.....                                                                         | 38 |

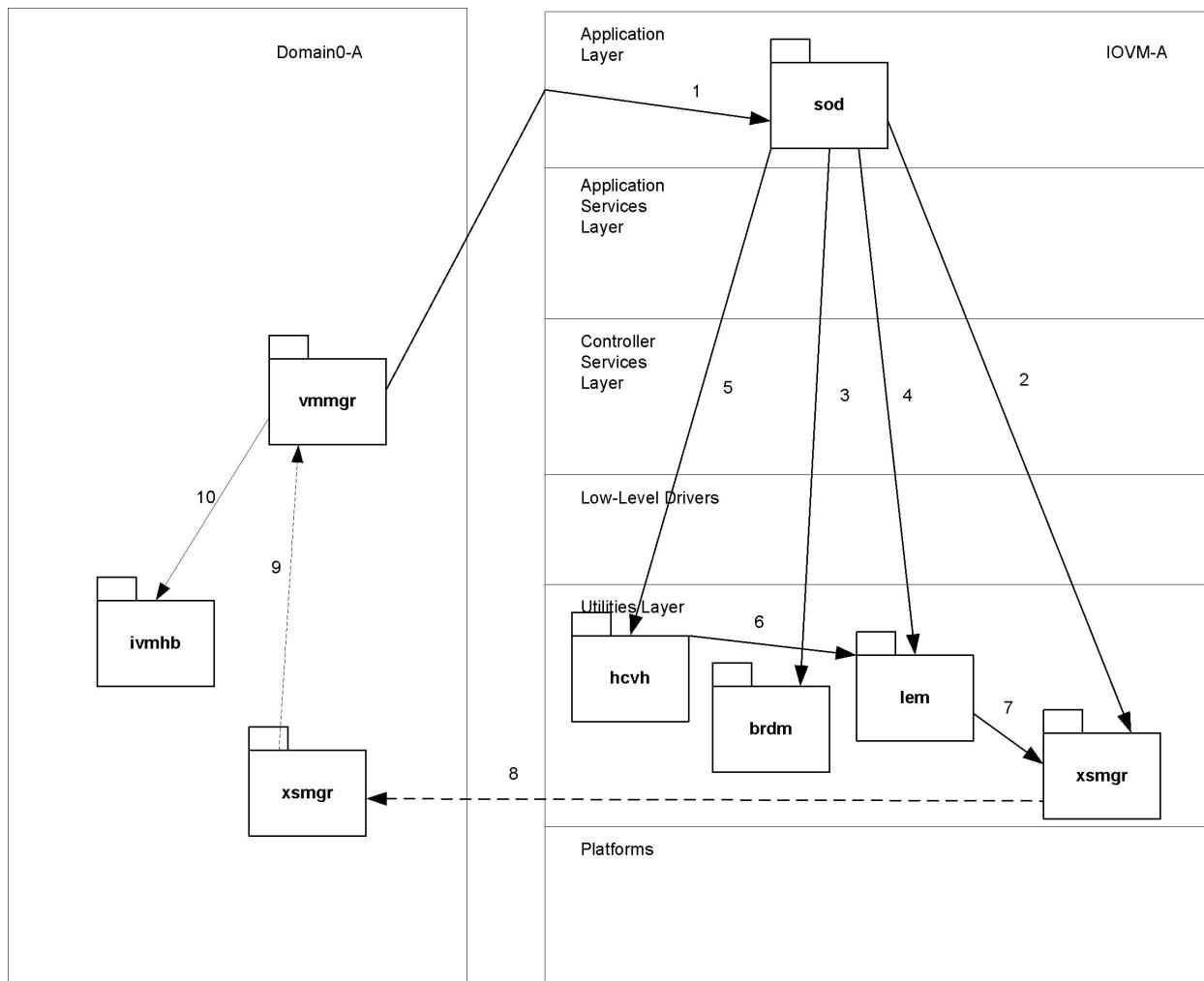

| 3.1.1.1.4.2. SBB Validation Failure.....                                                                         | 40 |

| 3.1.1.1.5. Controller Type Mismatch.....                                                                         | 42 |

| 3.1.1.1.5.1. Scenario 1 (Alternate controller is up and internal NIC is working normally).....                   | 42 |

| 3.1.1.1.5.2. Scenario 2 (Alternate controller is physically in-place but running late).....                      | 42 |

| 3.1.1.1.5.3. Scenario 3 (Alternate controller is physically in-place but not responding in a timely manner)..... | 43 |

| 3.1.1.1.5.4. Scenario 4 (Alternate controller is not in-place).....                                              | 44 |

| 3.1.1.1.5.5. Scenario 5 (Alternate controller is not in-place but inserted later).....                           | 44 |

| 3.1.1.1.5.6. Special Lockdown.....                                                                               | 45 |

| 3.1.1.1.6. Power Supply SBB validation and PMBus support.....                                                    | 46 |

| 3.1.1.1.7. HIC Support.....                                                                                      | 46 |

| 3.1.1.1.7.1. FC and InfiniBand.....                                                                              | 46 |

| 3.1.1.1.7.2. Glen Cove (iSCSI and Ethernet HIC).....                                                             | 47 |

| 3.1.1.1.7.2.1. Scenarios.....                                                                                    | 49 |

| 3.1.1.1.7.3. Controller Lockdown due to mismatch or unsupported HIC.....                                         | 52 |

| 3.1.1.1.7.4. Cache backup device diagnostics.....                                                                | 53 |

| 3.1.1.1.8. Verify DIMM configuration.....                                                                        | 53 |

| 3.1.1.1.9. Disable USB Port.....                                                                                 | 54 |

| 3.1.1.1.10. Push Button Support.....                                                                             | 55 |

| 3.1.1.1.11. SATA Flash handling.....                                                                             | 55 |

| 3.1.1.1.11.1. Flash Layout record.....                                                                           | 55 |

| 3.1.1.1.11.2. Flash partitioning.....                                                                            | 55 |

| 3.1.1.1.11.3. Default Boot Partition.....                                                                        | 55 |

| 3.1.1.1.11.4. Invalid SATA flash disk configurations.....                                                        | 55 |

| 3.1.1.1.12. CPU Temperature Monitoring.....                                                                      | 58 |

| 3.1.1.1.12.1. Setting CPU Threshold Temperature.....                                                             | 58 |

| 3.1.1.1.12.2. CPU over temperature condition (Threshold # 1) detected.....                                       | 60 |

| 3.1.1.1.12.3. Abatement of CPU over temperature condition (Threshold # 1).....                                   | 62 |

| 3.1.1.1.12.4. CPU over temperature condition (Threshold # 2) detected.....                                       | 62 |

| 3.1.1.1.13. ECC error handling.....                                                                              | 62 |

| 3.1.1.1.14. PCI/PCIe error handling.....                                                                         | 62 |

| 3.1.1.1.15. Wake On LAN (WOL).....                                                                               | 62 |

| 3.1.1.1.16. NTB.....                                                                                             | 62 |

| 3.1.2. Core Assets.....                                                                                          | 62 |

| 3.1.2.1. Core Application Services.....                                                                          | 63 |

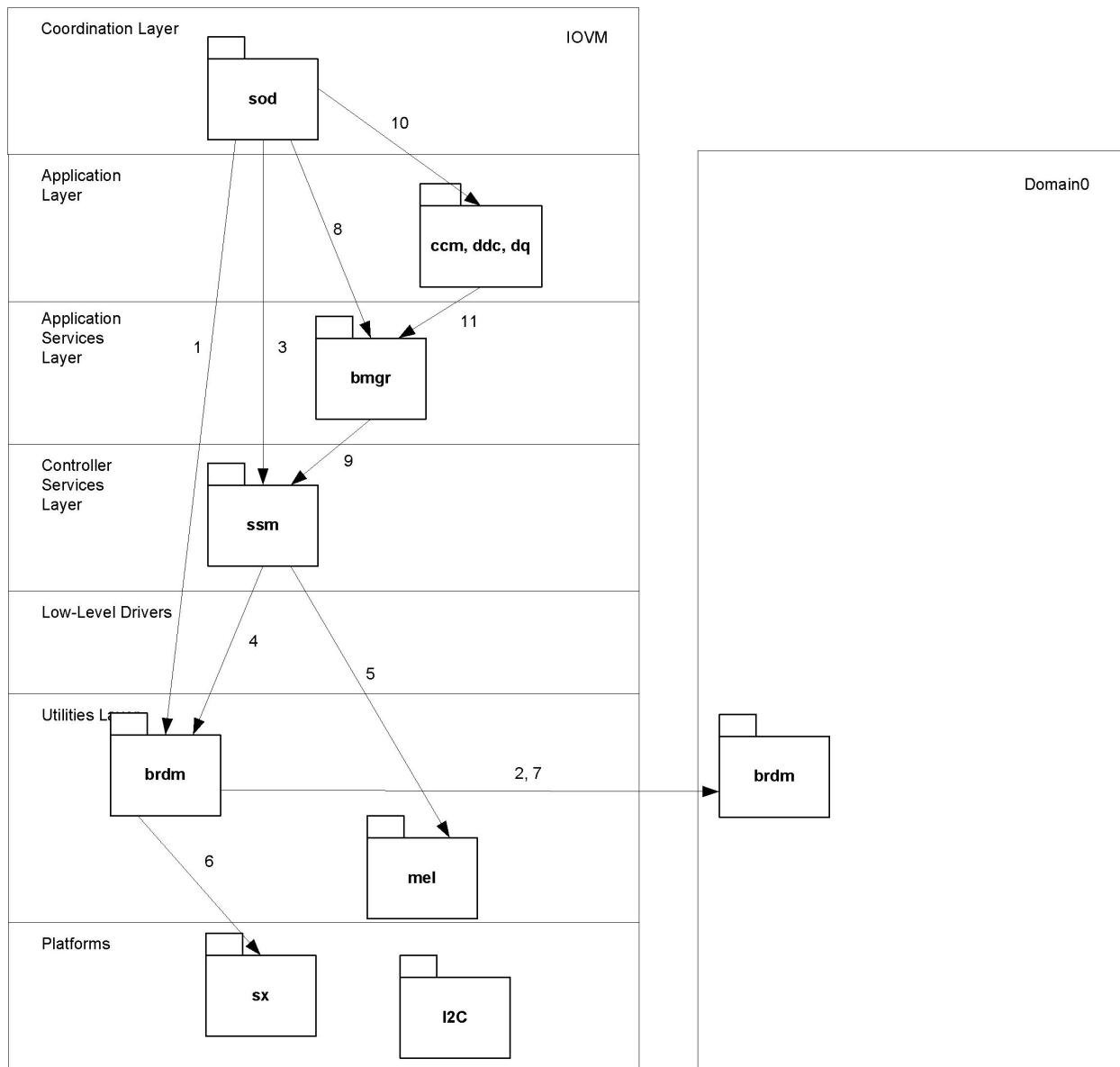

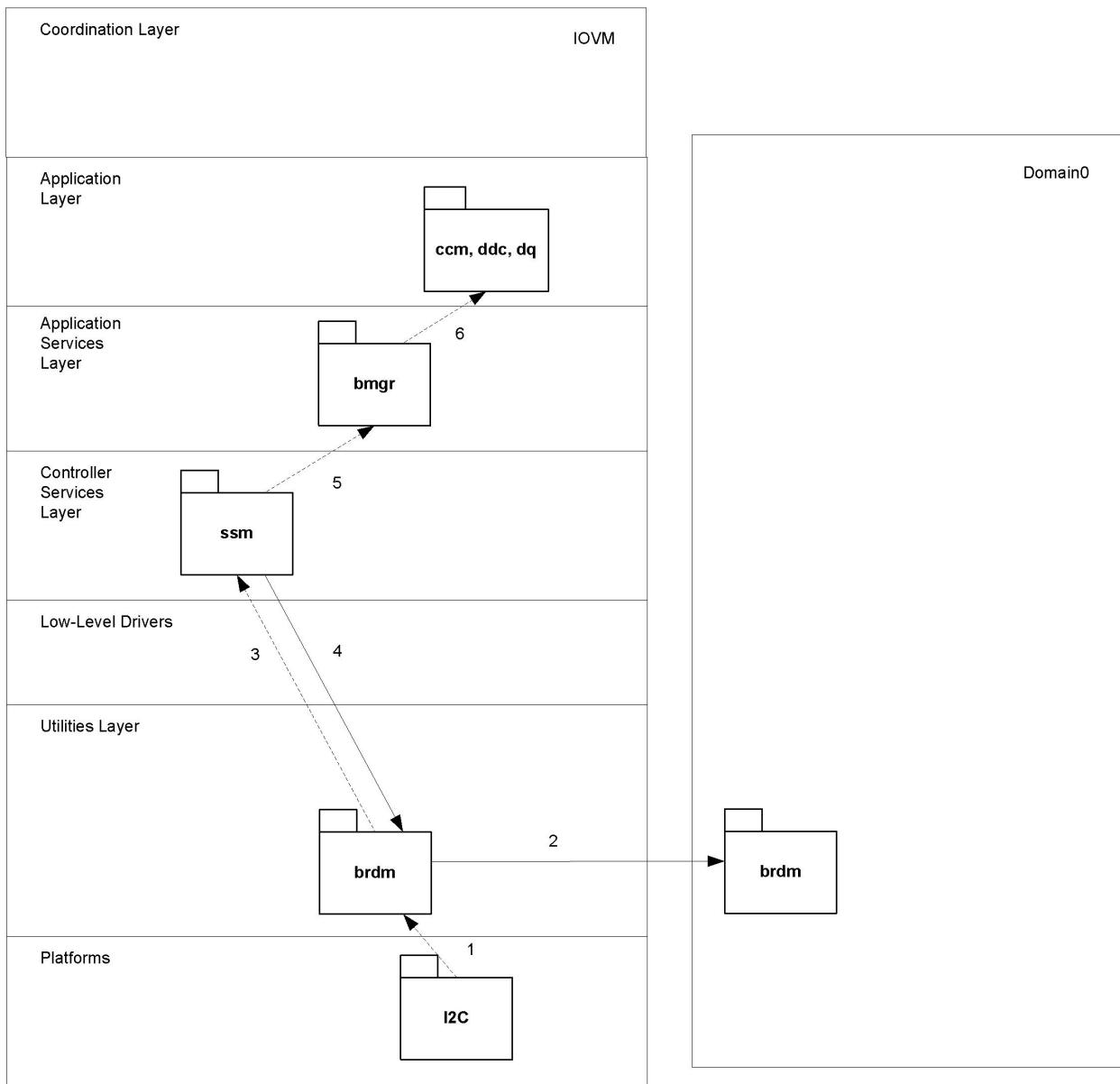

| 3.1.2.1.1. [IOVM] brdm - Board Manager.....                                                                      | 63 |

| 3.1.2.1.2. [Domain0] brdm - Board Manager.....                                                                   | 63 |

| 3.1.2.1.3. [IOVM] ssm - Sub System Monitor.....                                                                  | 63 |

| 3.1.2.1.4. [IOVM] hcvh - Hardware Configuration Validation Handler.....                                          | 64 |

|                                                                            |    |

|----------------------------------------------------------------------------|----|

| 3.1.2.1.5. [Domain0] hcvh - Hardware Configuration Validation Handler..... | 64 |

| 3.1.2.2. Diagnostic Services.....                                          | 64 |

| 3.1.2.2.1. [IOVM] bcdm - Base Controller Diagnostics Manager.....          | 64 |

| 3.1.2.3. Firmware Architecture.....                                        | 64 |

| 3.1.2.3.1. VariationMgmt – Variation Management Tools.....                 | 64 |

| 3.1.2.3.1.1. Gears Variable.....                                           | 64 |

| 3.1.2.3.1.1.1. hostboard::Supported Boards.....                            | 64 |

| 3.1.2.3.1.2. Module and Mixin:.....                                        | 65 |

| 3.1.2.3.1.2.1. Hostboard.....                                              | 65 |

| 3.1.2.3.1.3. Recipe Process.....                                           | 67 |

| 3.1.2.4. Foundations 1.....                                                | 67 |

| 3.1.2.4.1. [IOVM] SYMBol API.....                                          | 67 |

| 3.1.2.4.2. [IOVM] Meldb – Major Event Log Database.....                    | 67 |

| 3.1.2.4.2.1. Invalid SATA flash disk configurations.....                   | 67 |

| 3.1.2.4.2.2. CPU Thermal Control Circuit activated.....                    | 68 |

| 3.1.2.5. Foundations 2.....                                                | 68 |

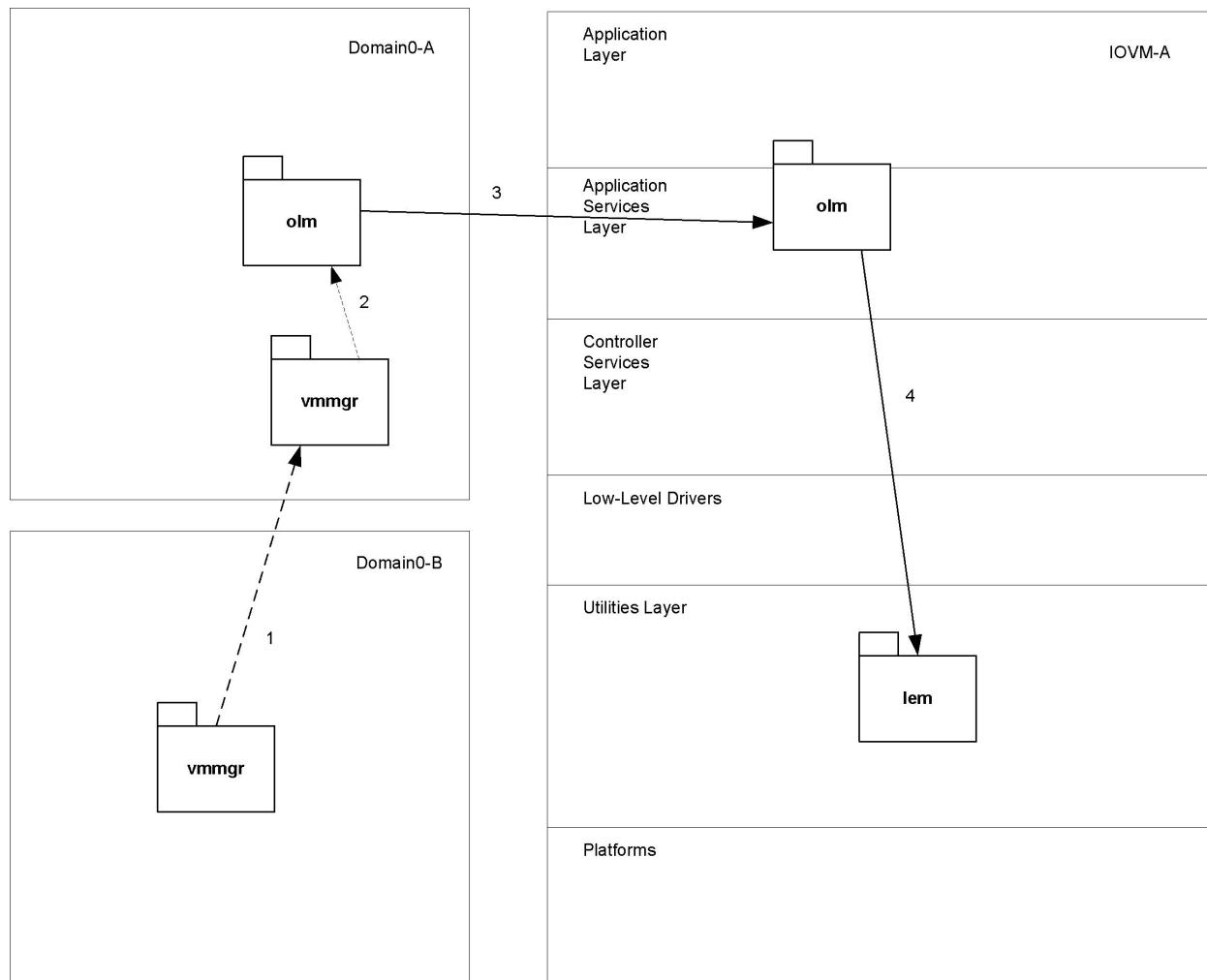

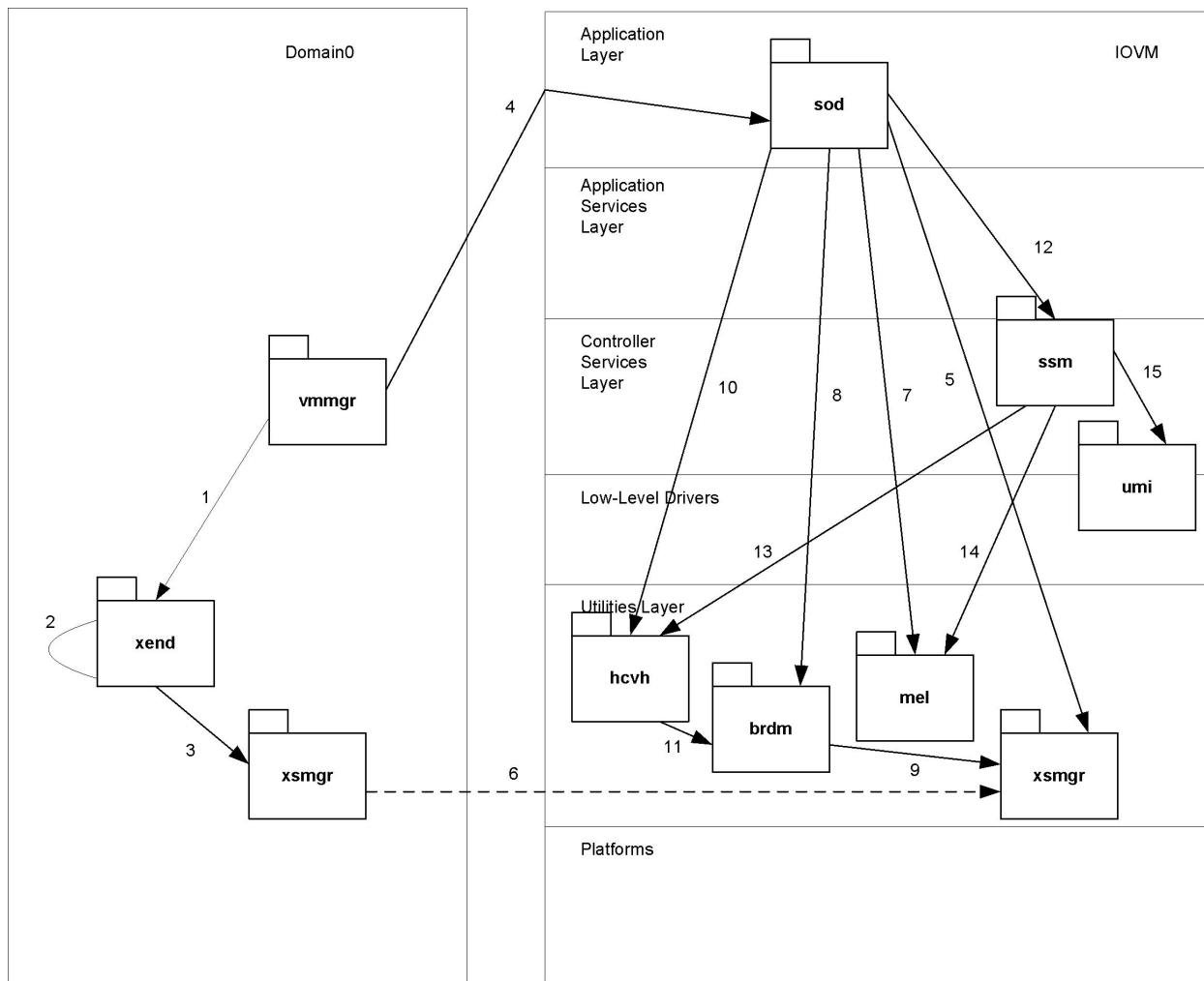

| 3.1.2.5.1. [Domain0] vmmgr - Virtual Machine Manager.....                  | 68 |

| 3.1.2.5.2. [Domain0] olm - OSA Lockdown Manager.....                       | 69 |

| 3.1.2.5.3. [Domain0] fpmgr - Flash Partition Manager.....                  | 69 |

| 3.1.2.5.4. [IOVM] cmgr – Controller Manager.....                           | 69 |

| 3.1.2.5.5. [IOVM] lem - Lockdown Error Manager.....                        | 69 |

| 3.1.2.6. IO Interfaces 1.....                                              | 69 |

| 3.1.2.6.1. [IOVM] ioni - I/O Network Interface.....                        | 69 |

| 3.1.2.7. IO Interfaces 3.....                                              | 70 |

| 3.1.2.7.1. [IOVM] isni - iSCSI Network Interface.....                      | 70 |

| 3.1.2.7.2. [IOVM] b_isn - Breckenridge iSCSI network Manager.....          | 70 |

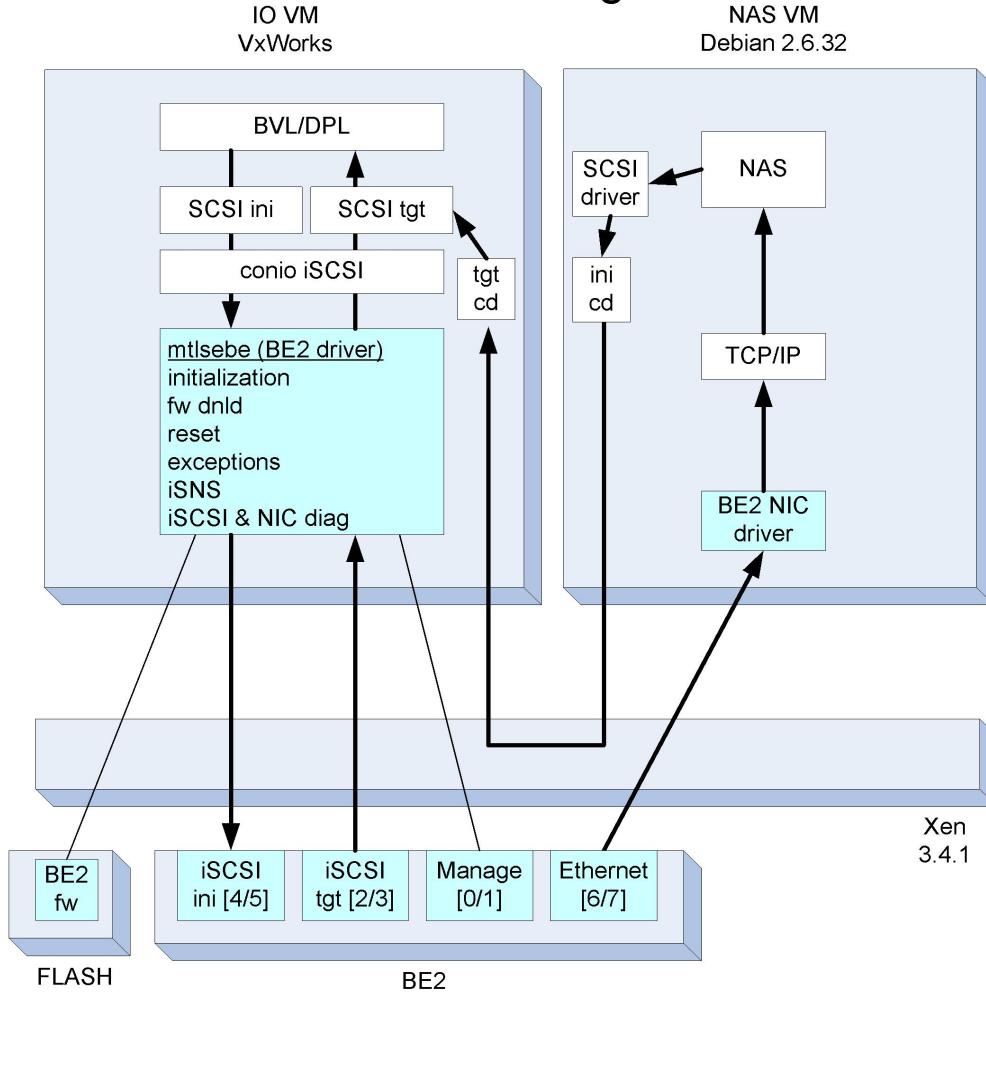

| 3.1.2.7.3. [IOVM] mtlsebe.....                                             | 70 |

| 3.1.2.7.4. [IOVM] be2nic.....                                              | 70 |

| 3.1.2.8. IO Interfaces 4.....                                              | 70 |

| 3.1.2.8.1. [IOVM] ib_hw – IB Hardware Specific Driver.....                 | 71 |

| 3.1.2.8.2. [IOVM] ib_core – InfiniBand Core Driver.....                    | 71 |

| 3.1.2.8.3. [IOVM] ibHcaFw – InfiniBand HCA Firmware Image.....             | 71 |

| 3.1.2.8.4. [IOVM] LCL – Linux Compatibility Layer.....                     | 71 |

| 3.1.2.8.5. [IOVM] STP_SRP – SCSI RDMA Protocol.....                        | 71 |

| 3.1.2.9. Platforms.....                                                    | 71 |

| 3.1.2.9.1. [IOVM] BCM – Board Configuration Module.....                    | 71 |

| 3.1.2.9.2. [IOVM] common – Common PCI Definitions.....                     | 71 |

| 3.1.2.9.3. [IOVM] Diag – Diagnostic Platform Module.....                   | 71 |

| 3.1.2.9.4. [IOVM] mpm - Midplane Manager.....                              | 72 |

| 3.1.2.9.5. [IOVM] pwsplm - Power Supply Manager.....                       | 72 |

| 3.1.2.9.6. BIOS.....                                                       | 72 |

| 3.1.2.10. Volume IO Services.....                                          | 72 |

| 3.1.2.10.1. [IOVM] ccm - Cache Configuration Manager.....                  | 72 |

| 3.1.2.10.2. [IOVM] rpa - RAID Parity Assist.....                           | 72 |

| 3.1.2.10.3. [IOVM] cache - Cache Management.....                           | 72 |

| 3.1.2.10.4. [IOVM] pbm - Persistent Backup Manager.....                    | 72 |

---

|                                                               |    |

|---------------------------------------------------------------|----|

| 3.1.2.11. Hypervisor.....                                     | 73 |

| 3.1.2.11.1. [Domain0] ivmhb - Inter VM Heartbeat Manager..... | 73 |

| 3.1.2.11.2. XenStore Key/Values.....                          | 73 |

## LIST OF FIGURES

|                                                                |    |

|----------------------------------------------------------------|----|

| Figure 1: Pikes Peak SBB 2.0 Controller.....                   | 12 |

| Figure 2: Retrieve Alternate controller's Baseboard ID.....    | 36 |

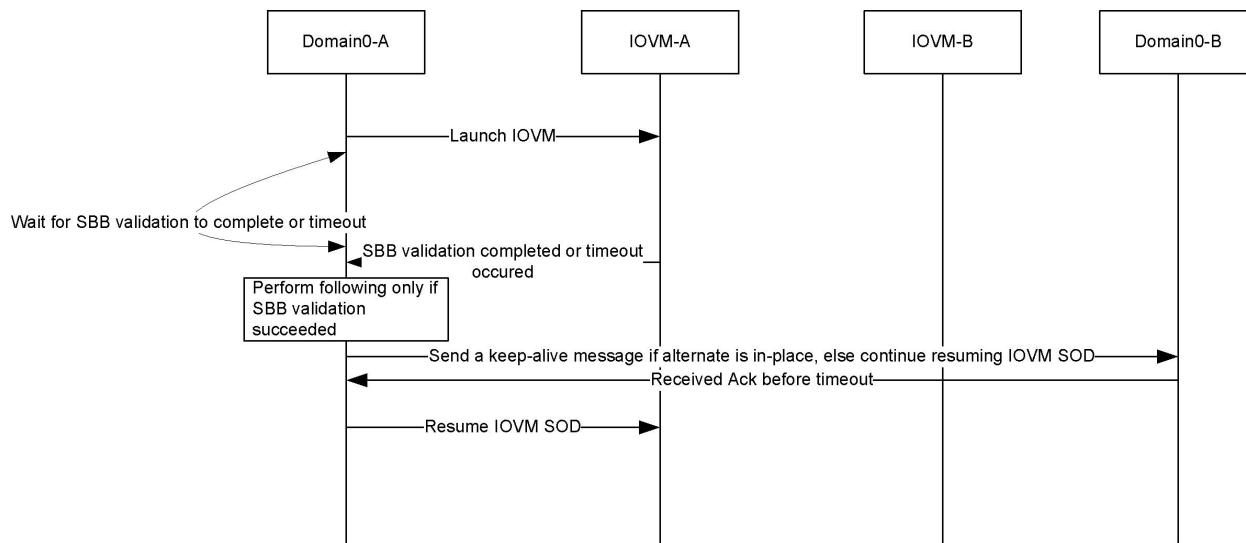

| Figure 3: SBB Validation success sequence relative to SOD..... | 38 |

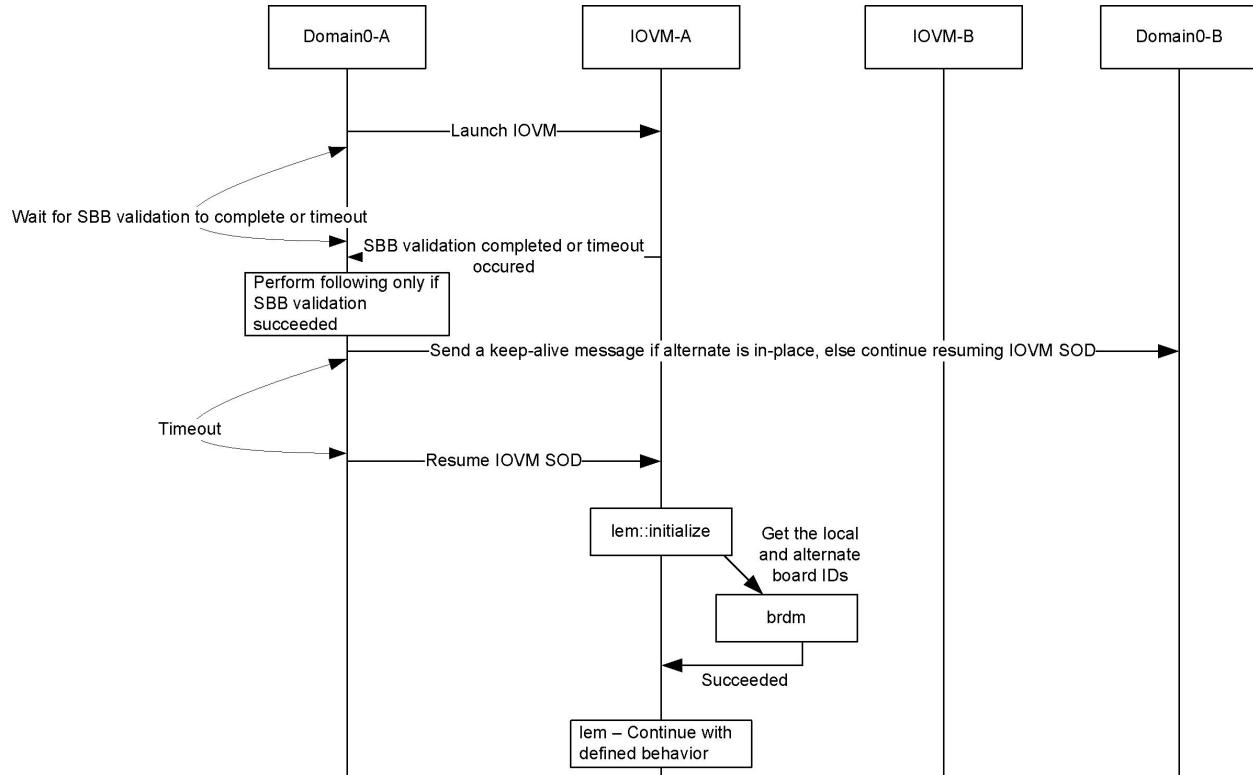

| Figure 4: SBB Validation failure sequence relative to SOD..... | 40 |

| Figure 5: Controller Type Mismatch - Scenario 1.....           | 42 |

| Figure 6: Controller Type Mismatch - Scenario 2.....           | 43 |

| Figure 7: Controller Type Mismatch - Scenario 3.....           | 43 |

| Figure 8: Controller Type Mismatch - Scenario 5.....           | 44 |

| Figure 9: PCI function assignments for Glen Cove.....          | 47 |

| Figure 10: DIMM Verification.....                              | 53 |

| Figure 11: SATA flash disk configuration validation.....       | 56 |

| Figure 12: Setting CPU temperature threshold values.....       | 58 |

| Figure 13: CPU Over temperature condition detected.....        | 60 |

## LIST OF TABLES

|                                                                                      |    |

|--------------------------------------------------------------------------------------|----|

| Table 1: Pikes Peak Host Interface (On base board) Characteristics.....              | 18 |

| Table 2: Pikes Peak Drive Interface Characteristics.....                             | 19 |

| Table 3: Pikes Peak General Controller Characteristics.....                          | 19 |

| Table 4: Pikes Peak Controller Identifiers and Model Names.....                      | 21 |

| Table 5: Pikes Peak Controller Smart Battery Configuration.....                      | 22 |

| Table 6: Pikes Peak Controller Smart Battery Attributes.....                         | 22 |

| Table 7: Pikes Peak Controller Smart Battery Temperature Logging Ranges (deg C)..... | 22 |

| Table 8: Pikes Peak Component Failure Identification.....                            | 23 |

| Table 9: Pikes Peak Protection Information Capability.....                           | 24 |

| Table 10: Cache Backup Device Partition.....                                         | 30 |

| Table 11: Ctlr Lockdown scenario due to HICs.....                                    | 53 |

| Table 14: XenStore Key/Values.....                                                   | 73 |

## Source Document Information

- Section 1. Pikes Peak hardware platform - An Overview

- Section 2.1. Pikes Peak hardware platform - Element Requirements

- Section 2.2. Controller Type Mismatch - Element Requirements

- Section 2.3. Host Interface Cards - Element Requirements

- Section 2.4. SATA Flash Disk Support - Element Requirements

- Section 2.5. Auto MDIX - Element Requirements

- Section 2.6. ECC and PCI Error Handling - Element Requirements

- Section 2.7. Wake on LAN Support - Element Requirements

- Section 3.1. Pikes Peak hardware platform - Detailed Architecture

### Section 1. Pikes Peak hardware platform - An Overview

Type: overview

Document: 45555-00

Revision: A.4

Revision Date: 3/22/2010

Author(s): Ashish Batwara

## REVISION HISTORY

| Revision | Description of Changes                                                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A.4      | Incorporated comments from summit and issues discovered so far. The tool has issues with track changes enabled and hence changes are without track changes enabled. |

| A.3      | Incorporated review comments                                                                                                                                        |

| A.2      | Incorporated Review comments                                                                                                                                        |

| A.1      | Initial revision.                                                                                                                                                   |

### Section 2.1. Pikes Peak hardware platform - Element Requirements

Type: requirement

Document: 00000-00

Revision: A.3

Revision Date: 3/22/2010

Author(s): Ashish Batwara

## REVISION HISTORY

| Revision | Description of Changes       |

|----------|------------------------------|

| A.4      | Incorporated review comments |

| Revision | Description of Changes       |

|----------|------------------------------|

| A.3      | Incorporated review comments |

| A.2      | Incorporated Review Comments |

| A.1      | Initial revision.            |

## Section 2.2. Controller Type Mismatch - Element Requirements

Type: requirement

Document: 45552-00

Revision: A.4

Revision Date: 3/22/2010

Author(s): Ashish Batwara

## REVISION HISTORY

| Revision | Description of Changes                            |

|----------|---------------------------------------------------|

| A.4      | Incorporated the comments from discussions so far |

| A.3      | Incorporated review comments                      |

| A.2      | Incorporated review comments                      |

| A.1      | Initial revision.                                 |

## Section 2.3. Host Interface Cards - Element Requirements

Type: requirement

Document: 44339-00

Revision: A.3

Revision Date: 3/21/2010

Author(s): Ashish Batwara, Jim Lynn

## REVISION HISTORY

| Revision | Description of Changes        |

|----------|-------------------------------|

| A.3      | Glen cove supports 10 GB only |

| A.2      | Incorporated Review comments  |

| A.1      | Initial revision.             |

## Section 2.4. SATA Flash Disk Support - Element Requirements

Type: requirement

Document: 45550-00

Revision: A.3

Revision Date: 3/22/2010

Author(s): Ashish Batwara

## REVISION HISTORY

| Revision | Description of Changes                                                                     |

|----------|--------------------------------------------------------------------------------------------|

| A.4      | Incorporated review comments. There are many open items and items under Architecture note. |

| A.3      | Incorporated review comments                                                               |

| A.2      | Incorporated Review comments                                                               |

| A.1      | Initial revision.                                                                          |

### Section 2.5. Auto MDIX - Element Requirements

Type: requirement

Document: 44889-00

Revision: A.1

Revision Date: 3/21/2010

Author(s): Aaron Dailey, Ashish Batwara

## REVISION HISTORY

| Revision | Description of Changes |

|----------|------------------------|

| Revision | Description of Changes |

| A.1      | Initial revision.      |

### Section 2.6. ECC and PCI Error Handling - Element Requirements

Type: requirement

Document: 44539-00

Revision: A.3

Revision Date: 3/21/2010

Author(s): Ashish Batwara, Aaron Dailey

## REVISION HISTORY

| Revision | Description of Changes       |

|----------|------------------------------|

| A.3      | Incorporated review comments |

| A.2      | Incorporated Review comments |

| A.1      | Initial revision.            |

## Section 2.7. Wake on LAN Support - Element Requirements

Type: requirement

Document: 00000-00

Revision: A.1

Revision Date: 3/21/2010

Author(s): Ashish Batwara

## REVISION HISTORY

| Revision | Description of Changes |

|----------|------------------------|

| Revision | Description of Changes |

| A.1      | Initial revision.      |

## Section 3.1. Pikes Peak hardware platform - Detailed Architecture

Type: architecture

Document: 45555-00

Revision: A.4

Revision Date: 3/22/2010

Author(s): Ashish Batwara

## REVISION HISTORY

| Revision | Description of Changes                                                                                                       |

|----------|------------------------------------------------------------------------------------------------------------------------------|

| A.4      | Incorporated comments from summit and issues discovered so far. There are major changes in the rev, hence a cleaned version. |

| A.3      | Incorporated review comments                                                                                                 |

| A.2      | Incorporated review comments                                                                                                 |

| A.1      | Initial revision.                                                                                                            |

## 1. Pikes Peak hardware platform - An Overview

### 1.1. Aspect Introduction

#### 1.1.1. Aspect Description

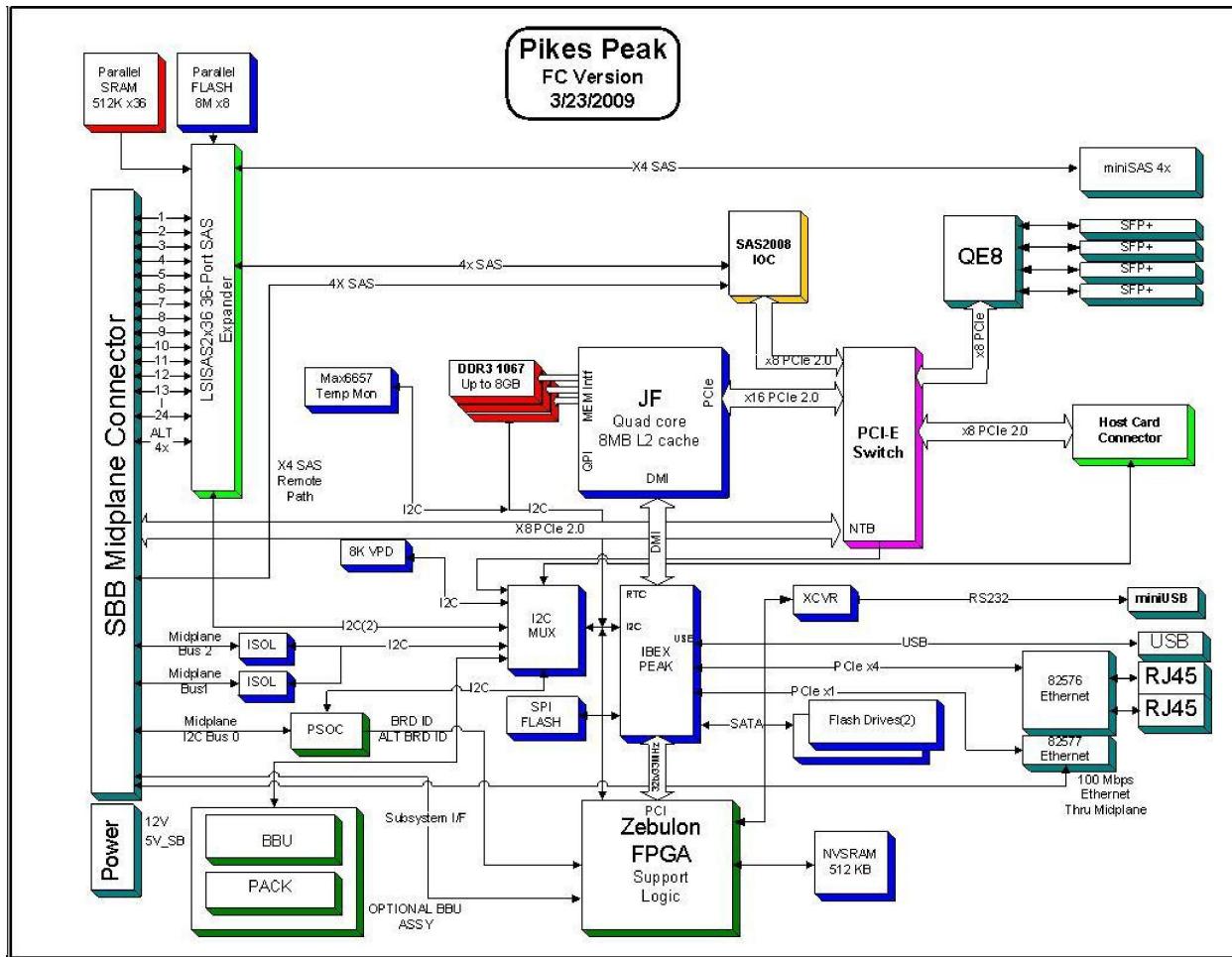

The Pikes Peak RAID Controller is designed for use in a SBB 2.0 Compliant Enclosure. The controller platform provides IA multi-core processor support and is designed for heterogeneous host connection to SAS 2.0 disk drives. On the host side it provides a quad 8 Gb/s Fibre Channel connection using an onboard Tachyon QE8 device. Other host connections are provided through a replaceable, modular host interface board.

The Pikes Peak RAID Controller core architecture consists of a multi-core Intel Jasper Forest (JF) Processor. The Jasper Forest Processor provides connection up to three Double Data Rate 3 Synchronous DRAM (DDR3 VLP SDRAM) memory DIMMs operating at up to 1067 MT/s. The Jasper Forest Processor also provides an x16 PCI Express Gen2 bus connection to a PCI Express Switch. Also connected to the PCI Express switch is a host board connector, a Tachyon QE8, the SBB midplane, and an LSISAS2008.

The Tachyon QE8 provides on-board Fibre Channel host connectivity. The SBB Midplane connection provides a high speed data path to an alternate controller for data mirroring. The LSISAS2008 chip provides a connection to the backend SAS expander chip and to alternate controller. An LSISAS2x36 Expander chip is utilized for the backend disk connections. The Pikes Peak controller is inserted into trays that contain internal drives; the number of drives is dependent upon the tray type and can support up to 60 disk drives. The Camden, Ebbets and SAS Wembley enclosures support Pikes Peak controller.

The Jasper Forest also connects to an Intel Ibex Peak platform controller hub (PCH). The main devices connected to the Ibex Peak are an Intel 82576, an Intel 82577, SATA Flash drives, and the Zebulon FPGA. The Intel 82576 provides two 1 Gb Ethernet management ports. The Intel 82577 provides a 100 Mb Ethernet connection to an alternate controller through the midplane. The SATA Flash drive(s) provide storage for a persistent cache offload when a power loss occurs. In addition to this, SATA flash drive(s) also provide storage for code, logs, configuration etc.

The Zebulon FPGA provides support logic for the Pikes Peak. Flexibility in host interface configurations is provided using replaceable host interface boards. The Pikes Peak Controller does not operate in simplex mode.

Figure 1: Pikes Peak SBB 2.0 Controller

The Pikes Peak Controller is offered in two versions to cover different price points and performance requirements. The two versions are referred to as PP400 and PP200. The PP400 is the high end controller and the PP200 is the low end controller.

The Pikes Peak controller has the following major components:

- Processor: The PP400 has SKU-4 of the Jasper Forest processor, which is a quad-core 2.13GHz Nehalem based processor with SMP. The PP200 has SKU-10 of the Jasper Forest processor, which is a dual-core 1.73GHz Nehalem based processor with SMP, supports Hyper-threading with VT capability.

- Host Ports on baseboard: Four on-board host side FC ports provided by Tachyon QE8.

- Host Interface Card (HIC): One HIC per controller. HIC can be of the following types:

1. Dual-port 40Gbps InfiniBand Host Interface (Elk Park)

2. Dual-port 10 GbE (iSCSI-SFP+ optical) iSCSI Host Interface (Glen Cove)

3. Quad-port 2/4/8 Gbps FC Host Interface (Manitou)

- DIMM: Up to 24 GB of 64-bit DDR3 SDRAM. The PP400 supports three DIMMs of either 4 GB or 8 GB. The PP200 supports two DIMMs of either 2 GB or 4 GB. The DIMMs on a controller must have to be of same capacity.

- Local Disk Drives: Pikes Peak supports up to 60 local SAS disk drives.

- Drive Channels: The Pikes Peak controller has 1 drive side channel which can be connected to

expansion trays.

- miniUSB: The Pikes Peak controller has 1 miniUSB connector which can be used during manufacturing or extreme-field debugging situations. It carries RS-232 connections.

- USB 2.0: The USB port on controller is used for manufacturing purpose. In a production environment, the USB port is unsupported and a device plugged into USB port is not recognized.

- The Pikes Peak controller has 1 USB connector which can be used during manufacturing or extreme-field debugging situations. This port can also be used to plug-in bootable USB drive. The USB device is not reported in object graph.

- SPI Flash: The SPI flash is of capacity 8 MB and connected to Ibex Peak SPI interface. This flash is having BIOS code for initial boot-up.

- NVSRAM: The Pikes Peak controller has NVSRAM of capacity 512 KB. It is behind Zebulon FPGA.

- SATA flash drives: The PP200 and PP400 have two SATA flash drives of capacity 8 GB for a total of 16 GB.

- FPGA: It is called Zebulon. It has three PCI functions. The function F0 and F2 map general purpose registers and NVSRAM. The function F1 maps UART. The function F2 is having duplicate mapping of general purpose registers required to route specific interrupts to appropriate virtual machine, i.e. Domain0 on Pikes Peak.

- Ethernet Ports: The Pikes Peak controller has two 1G external Ethernet ports for management purpose. The Ethernet port supports Auto MDIX, a mechanism by which NIC automatically detects the cable type (crossover v/s conventional) and handle. The Pikes Peak controller also has one 100 mbps internal Ethernet port to connect to alternate controller via midplane.

- The Pikes Peak controller has various LEDs managed by controller firmware:

1. Cache Active LED

2. Service Action Allowed LED (blue)

3. Service Action Required LED (amber)

4. BBU charging LED (green)

5. BBU service action LED (amber)

- Two seven-segment displays.

- Smart BBU. The gas gauge type is bq20z70.

- RAID 5 XOR, RAID6 (P+Q) hardware acceleration.

- A pushbutton switch to reset the IP address or setup initial configuration. At boot time, pressing this button changes the boot order preference.

- PCIE to PCIE NTB to support memory mirroring between controllers.

The Pikes Peak controller will be installed in SBB 2.0 compliant Camden, Ebbets or Wembley SAS enclosures.

### 1.1.2.Assumptions

- It is assumed that simplex mode is not required to be supported.

- The document 44540-00, Pikes Peak controller – IOVM specific changes, is prerequisite to this document.

### 1.1.3.Related Documents

| Document Number | Name of Document                          |

|-----------------|-------------------------------------------|

| 349-1051890     | SYMBOL Specification – Internal Master    |

| 37021-00        | Field Replaceable Host Interface Card FAM |

| 41692-00        | XBB-2 FRU Failure Reporting               |

| Document Number | Name of Document                                                        |

|-----------------|-------------------------------------------------------------------------|

| 41598-00        | XBB-2 Controller FRU Diagnostics                                        |

| 44327-00        | Pikes Peak FPGA Management                                              |

|                 | Hypervisor AAD                                                          |

| 42286-00        | Camden Ebbets Enclosure Support FAM                                     |

| 44338-00        | Wembley SAS Enclosure FFD                                               |

| 45787-00        | Wembley SAS Enclosure FAM                                               |

| 42061-00        | Zebulon FPGA - Hardware Functional Specifications                       |

| 42047-00        | Pikes Peak RAID Controller - Hardware Functional Specifications         |

| 41115-00        | Pikes Peak - Architectural Requirement Document (ARD)                   |

|                 | OSA CAS (Open Storage Architecture Concept Architecture Specifications) |

|                 | USP PAS (Unified Storage Platform Product Architecture Specifications)  |

| 349-1057240     | Component Location Reporting FFD                                        |

| 349-1056330     | Controller Management FFD                                               |

| 349-1053460     | Controller Type Mismatch FFD                                            |

| 349-1057430     | Persistent Cache Backup FFD                                             |

| 349-1063100     | Field Replaceable Cache Memory FFD                                      |

| 349-1053340     | Fan and Thermal Sensor Management FFD                                   |

| 46722-00        | Orion SOD and Component Architecture AAD                                |

### 1.1.4. Open Issues

- NTB specific details to be covered.

- ECC/PCIe error handling requirements are clear, but detailed architecture is still open due to POCs around it.

- Wake On LAN requirements and detailed architecture.

- Default value of Smart Battery Parameters is TBD.

- Define different seven-segment codes in BIOS for various boots such as PXE, USB, SATA flash etc?

- LSI specific signature to differentiate LSI specific USB boot drive and SATA flash drive.

Corresponding checking in BIOS needs to be done to lockout USB, SATA flash drive not having LSI specific signature. In other words, BIOS must ensure secure boot from devices such as USB, SATA flash, and PXE. It should stop booting if it does not recognize LSI firmware image.

- Do we need to support 1G mode in Glen Cove?

- AAD does not cover NAS (CIFS/NFS) functionality.

- CPU temperature threshold and fan failure - It seems XBB2 has this behavior. This is something when a fan fails in a normal running controller. Is it something beyond what is specified in this AAD as part of CPU temperature monitoring?

- CPU temperature Threshold # 1 and Threshold # 2.

- There are many open issues related to SATA flash disk requirements and corresponding functionalities. Most of those issues are documented with "Architecture Note" section in this AAD.

### 1.1.5.AAD References

The intent of this section is to document functionality that is referenced in this AAD that belongs to other AADs.

| Functionality                                       | Owned AAD/FFD Element                              | Referenced in this AAD                        |

|-----------------------------------------------------|----------------------------------------------------|-----------------------------------------------|

| Boot Process, especially PXE                        | Serviceability AAD - PXE ER                        | Push Button Support Section                   |

| Dual Controller Swap                                | Serviceability AAD - ACS and Controller Sparing ER | Dual Controller Swap                          |

| Lockdown behavior due to HIC and baseboard mismatch | Serviceability AAD - Controller State Management   | Start-of-Day Mismatch Detection               |

| IB HIC LED indicators                               | Controller Module Indicators FFD                   | InfiniBand Host Interface Card (Elk Park)     |

| SATA Flash disk management and replacement          | Serviceability AAD - System Diagnostics ER         | Disk Management and Replacement               |

| Power Supply SBB validation                         | SBB2 VPD Data Support FFD                          | Power Supply SBB validation and PMBus support |

| Cache Backup Device Diagnostics                     | Serviceability AAD - System Diagnostics ER         | Cache backup device diagnostics               |

## 1.2.Aspect High Level Requirements

### 1.2.1.Product Requirements

This document covers the element requirements and detailed architecture for following PRs:

| ClearQuest PR Number | Feature Name                                                   |

|----------------------|----------------------------------------------------------------|

| LSIP200009298        | Orion: Support 40Gb IB HIC on Pikes Peak SBB                   |

| LSIP200009299        | Orion: Support 8Gb FC HIC on Pikes Peak SBB                    |

| LSIP200011980        | Orion: Pikes Peak SAS Expander checks power supply at power up |

| LSIP200012568        | Orion: Management Ethernet ports should use Auto-MDIX          |

| LSIP200012572        | Orion: SATA Flash disk requirements                            |

| ClearQuest PR Number | Feature Name                                                          |

|----------------------|-----------------------------------------------------------------------|

| LSIP200012575        | Orion: Support LSI's PMBus implementation for power supply management |

| LSIP200012577        | Orion Use Linux's support for ECC/PCI error detection                 |

| LSIP200038257        | Orion: Wake On LAN Support WOL for Pikes Peak                         |

In addition to above PRs, this AAD also describes the controller type mismatch behavior on Pikes Peak.

### 1.2.2.AAD Overview

This AAD discusses (or plan to discuss) following major topics:

- Pikes Peak SBB hardware,

- The host interface cards supported

- SBB validation

- Controller type mismatch handling

- SATA Flash disk - Layout, SATA flash disk management, and disk replacement

- Ethernet Auto MDIX support

- ECC/PCIe error handling in OSA environment

- Wake On LAN support on Pikes Peak

- NTB support on Pikes Peak

- DIMM configuration verification

- CPU temperature monitoring

- Controller and Host Board ID computation and necessary infrastructure

## 2. Pikes Peak Controller - Element Requirements

### 2.1. Pikes Peak hardware platform - Element Requirements

#### 2.1.1. Introduction

This document provides the following controller specific information:

- Supported hardware configurations.

- Supported memory capacities.

- Handling field replaceable memory and persistent cache backup devices.

- Supported IP address Reset Push button.

#### 2.1.2. Operational Behavior

The Pikes Peak controller is a SBB 2.0 compliant controller supporting heterogeneous host connections such as iSCSI, FC, and InfiniBand (IB). It also supports drive side connections to SAS 2.0 disk drives. Pikes Peak base controller has four on-board Fibre Channel (FC) ports for host connectivity. Each host port supports data rate of 2, 4, or 8 Gb/s and the connectivity to the host ports is provided through SFP+ interfaces. In addition to the FC ports, base board also has a slot to install an additional Host Interface Card (HIC). The Pikes Peak controller supports FC, IB, and iSCSI host connections through optional HICs. For a supported configuration HICs on both the controllers in an array must be of same type.

The Pikes Peak Controller is offered in two versions to cover different price points and performance requirements. The two versions are referred to as the PP400 and the PP200. The PP400 is the high end controller and the PP200 is the low end controller. Both the versions support existing tiered performance behavior. The PP200 and PP400 do not support simplex mode.

##### 2.1.2.1. Host Interface Characteristics

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDACCP5B

Table 1: Pikes Peak Host Interface (On base board) Characteristics

| Parameter      | Characteristic/Value                                                                 | Reference |

|----------------|--------------------------------------------------------------------------------------|-----------|

| Host Interface | 1 host interface card slot and four 2/4/8 Gb/s FC connections on the base controller | 1         |

References:

Document Number 349-1057870, the Feature Function Definition for Controller Host Interface Card Management

##### 2.1.2.2. Drive Interface Characteristics

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDACKP5B

Table 2: Pikes Peak Drive Interface Characteristics

| Parameter                                                                               | Characteristic/Value                | Reference |

|-----------------------------------------------------------------------------------------|-------------------------------------|-----------|

| Interface Type                                                                          | SAS                                 | 1         |

| Supported Link Rates (Gb/s)                                                             | 6 Gb/s                              | 1         |

| Number of Drive Channels                                                                | 1                                   |           |

| Drive Channel Port Location                                                             | Controller                          |           |

| Drive Channel Expansion Ports per Controller                                            | 1 (x4 port via integrated Expander) |           |

| References:                                                                             |                                     |           |

| 1. Document Number 349-1048660, the Feature Function Definition for SAS Drive Interface |                                     |           |

### 2.1.2.3. General Controller Characteristics

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDA5UP5B

Table 3: Pikes Peak General Controller Characteristics

| Parameter                                           | Characteristic/Value                                                                                   | Reference |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------|

| Memory System                                       | Three unified processor/cache memory DIMM on PP400<br>Two unified processor/cache memory DIMM on PP200 |           |

| Cache Persistence                                   | Persistent cache backup                                                                                | 1, 11     |

| Cache Backup Device                                 | SATA flash drive (2x8G on PP200 and PP400)                                                             |           |

| Cache Backup Power Source                           | Batteries                                                                                              | 11        |

| Cache Backup Power Coordination between controllers | Not Required                                                                                           | 11        |

| Dedicated Mirror Channels                           | Yes (NTB based - TBD)                                                                                  |           |

| Ethernet Management Ports                           | Two 10/100/1000 external ports, One 10/100 internal port                                               | 2, 3      |

| Seven-Segment Display                               | Yes                                                                                                    | 4         |

| Seven-Segment Display Sequences                     | Supported                                                                                              | 4         |

| Controller Enclosure Tray ID                        | Soft-set (Displayed on seven-                                                                          | 5         |

| Parameter                                                                                                    | Characteristic/Value                                 | Reference |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------|

|                                                                                                              | segment display)                                     |           |

| Audible Alarm on Controller Module                                                                           | No                                                   |           |

| Performance Tier                                                                                             | Supported                                            | 7         |

| Board Sub-Model Identifier                                                                                   | Supported                                            | 7         |

| Field Replaceable Cache Memory                                                                               | Yes (Shared memory)                                  | 9         |

| Processor/Cache DIMM Lock-down Recovery                                                                      | Manual                                               |           |

| Discrete Line Test Capability                                                                                | No                                                   | 10        |

| CPU Die Temp Sensor                                                                                          | Yes (CPU temperature monitoring circuitry available) |           |

| Serial Port                                                                                                  | miniUSB                                              |           |

| USB Port                                                                                                     | Yes                                                  |           |

| Supported Enclosures                                                                                         | Camden, Ebbets, Wembley SAS                          | 12, 13    |

| IP Address Reset Push Button Support                                                                         | Yes                                                  |           |

| Auto MDIX support                                                                                            | Yes                                                  |           |

| Wake On LAN (WOL) support                                                                                    | Yes (TBD)                                            |           |

| References:                                                                                                  |                                                      |           |

| 1. Document Number 349-1056620, the Feature Function Definition for Cache Management                         |                                                      |           |

| 2. Document Number 27013-00, the Feature Function Definition for Gigabit Ethernet Management Port            |                                                      |           |

| 3. Document Number 27806-00, the Feature Function Definition for Ethernet Management Port IPv4 Configuration |                                                      |           |

| 4. Document Number 34533-00, the Feature Function Definition for Controller Module Indicators                |                                                      |           |

| 5. Document Number 349-1048590, the Feature Function Definition for Tray Identifier Management               |                                                      |           |

| 6. Document Number 349-1053220, the Feature Function Definition for Audible Alarm Management                 |                                                      |           |

| 7. Document Number 349-1049530, the Feature Function Definition for Tiered Performance Management.           |                                                      |           |

| 8. Document Number 349-1053830, the Feature Function Definition for Board Sub-Model Identifier               |                                                      |           |

| 9. Document Number 349-1063100, the Feature Function Definition for Field Replaceable Cache                  |                                                      |           |

| Parameter | Characteristic/Value | Reference                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory    |                      | 10. Document Number 349-1056330, the Feature Function Definition for Controller Management<br>11. Document Number 349-1057430, the Feature Function Definition for Persistent Cache Backup<br>12. Document Number 42197-00, the Feature Function Definition for DE1600/DE5600 Enclosure Support<br>13. Document Number 44338-00, the Feature Function Definition for DE6600 Enclosure Support |

### 2.1.2.4. Controller Identifiers

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAXEAIC

Table 4: Pikes Peak Controller Identifiers and Model Names

| Model Name | Base Board ID (Controller ID) | Host Card ID | Description                         | Host Ports                               |

|------------|-------------------------------|--------------|-------------------------------------|------------------------------------------|

| 5280       | 5268                          | None         | PP200 baseboard with no HIC         | Four 2/4/8 Gb/s FC                       |

| 5288       | 5268                          | 0801         | PP200 baseboard with FC HIC         | Eight 2/4/8 Gb/s FC                      |

| 5281       | 5268                          | 0101         | PP200 baseboard with iSCSI-SFP+ HIC | Four 2/4/8 Gb/s FC and two 10 Gb/s iSCSI |

| 5284       | 5268                          | 0401         | PP200 baseboard with IB HIC         | Four 2/4/8 Gb/s FC and two 40 Gb/s IB    |

| 5480       | 5468                          | None         | PP400 baseboard with no HIC         | Four 2/4/8 Gb/s FC                       |

| 5488       | 5468                          | 0801         | PP400 baseboard with FC HIC         | Eight 2/4/8 Gb/s FC                      |

| 5481       | 5468                          | 0101         | PP400 baseboard with iSCSI-SFP+ HIC | Four 2/4/8 Gb/s FC and two 10 Gb/s iSCSI |

| 5484       | 5468                          | 0401         | PP400 baseboard with IB HIC         | Four 2/4/8 Gb/s FC and two 40 Gb/s IB    |

### 2.1.2.5. Battery Management

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDA5YAIC

| Parameter     | Characteristic/Value |

|---------------|----------------------|

| Smart Battery | Yes                  |

| Parameter                             | Characteristic/Value                         |

|---------------------------------------|----------------------------------------------|

| Battery Identity Tracked              | Yes                                          |

| Battery Location                      | Controller Canister                          |

| Battery Removal Method                | Remove controller in order to remove battery |

| Battery Replacement Method            | Replace Self                                 |

| Battery Packaging                     | Dual individual CRUs                         |

| Total Battery packs                   | 2 (One per controller)                       |

| Default Expiration Age (90-day units) | 13 units (1170 days or 3.21 years)           |

### 2.1.2.6. Smart Battery Parameters

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAZCBIC

Reference: Document Number 349-1057690, the Feature Function Definition for Smart Battery Management.

Smart battery configuration parameters are described in the reference. If a parameter is set to zero, the default value is used. The units and default values are shown in the following tables:

Table 5: Pikes Peak Controller Smart Battery Configuration

| Parameter Name                     | Units   | Default   |

|------------------------------------|---------|-----------|

| Minimum Application Capacity       | Seconds | 80 (TBD)  |

| Replacement (Full Charge) Capacity | Seconds | 313 (TBD) |

| Learn Cycle Interval               | Weeks   | 8 (TBD)   |

Table 6: Pikes Peak Controller Smart Battery Attributes

| Attribute                                                            | Value |

|----------------------------------------------------------------------|-------|

| Cache during battery learn cycle                                     | TRUE  |

| Learn cycle terminated if critical BBU temperature threshold reached | FALSE |

| Charging disabled if critical BBU temperature threshold reached      | FALSE |

Table 7: Pikes Peak Controller Smart Battery Temperature Logging Ranges (deg C)

| Minimum Temperature | Maximum Temperature |

|---------------------|---------------------|

| No minimum          | 35                  |

| Minimum Temperature | Maximum Temperature |

|---------------------|---------------------|

| 36                  | 40                  |

| 41                  | 45                  |

| 46                  | 50                  |

| 51                  | 55                  |

| 56                  | 60                  |

| 61                  | 65                  |

| 66                  | 70                  |

| 71                  | No maximum          |

### 2.1.2.7. Seven Segment Display Support

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAO1BIC

Reference: Document Number 34533-00, the Feature Function Definition for Controller Module Indicators.

Pikes Peak controllers display category-detail sequences on a seven-segment display as described in the reference. The seven-segment display is used to identify controller component failures as indicated in table below. Component failures may also be identified through event notification mechanisms when the controller is in the operational state.

Table 8: Pikes Peak Component Failure Identification

| Component (Code)   | Seven-Segment Display used in this controller state |           |             |

|--------------------|-----------------------------------------------------|-----------|-------------|

|                    | Power-on diagnostics                                | Suspended | Operational |

| Shared DIMM (Dx+)  | Yes (Only on Cache portion)                         | Yes       | No          |

| Host Card (Hx+)    | Yes                                                 | Yes       | No          |

| Flash Drive (Fx+)  | Yes                                                 | No        | Yes         |

| Battery            | No                                                  | No        | No          |

| Power Supply (Sb+) | Yes                                                 | Yes       | No          |

**Architecture Note:** Do we perform Power-on diagnostics on Power Supplies on existing platforms? If so, does controller currently display 7-segment code for Power Supply power-on diagnostics failure on existing platforms?

### 2.1.2.8. Protection Information Capability

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDARICIC

Reference: Document Number 34472-00, the Feature Function Definition for End-to-End Data Protection Information (PI).

Table 9: Pikes Peak Protection Information Capability

| Base Board ID/Host Board ID | Description                                     | PI Capable |

|-----------------------------|-------------------------------------------------|------------|

| 5268, 5468                  | Base Pikes Peak Controller with 4 FC host ports | Yes        |

| 0801                        | 4-port 2/4/8 Gb/s FC HIC                        | Yes        |

| 0101                        | 2-port 10 Gb/s iSCSI-SFP+ HIC                   | Yes        |

| 0401                        | 2-port 40 Gb/s IB HIC                           | Yes        |

### 2.1.2.9. Field Replaceable Cache Memory

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAESIC

All DIMM slots in Pikes Peak controller shall have the same capacity DIMMs installed:

- PP200: Two DDR3-1067 DIMMs of capacity 2GB with a total capacity of 4GB

- PP200: Two DDR3-1067 DIMMs of capacity 4GB with a total capacity of 8GB

- PP400: Two DDR3-1067 DIMMs of capacity 4GB with a total capacity of 12GB

- PP400: Two DDR3-1067 DIMMs of capacity 8 GB with a total capacity of 24GB

The PP200 has 2 DIMM slots whereas PP400 has 3 DIMM slots. It is required that controllers have DIMMs of same capacity installed in available DIMM slots. DIMMs of different capacity on a controller are treated as unsupported. The unsupported behavior is same as described in document # 349-1063100, Field Replaceable Cache Memory Feature Function Definition.

### 2.1.2.10. Field Replaceable Cache Backup Device

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDARVCIC

The PP200 and PP400 have two cache backup devices, each of capacity 8 GB, populated in slot 0 and slot 1. Any configurations outside of these are considered invalid.

The controller has following behavior in case of invalid cache backup device configurations:

- The two controllers switch all volumes configured for write-back caching with mirroring to write-through caching.

- The controller continues to report all the installed cache backup devices.

- The controller logs a critical event and raises needs condition to add/remove the extra cache backup device.

Refer to SATA Flash Disk Element Requirement document for detailed information.

### 2.1.2.11. Field Replaceable HICs

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAPYCIC

The HICs on Pikes Peak controllers are field replaceable but HICs on both the controllers must match for the supported configuration.

Refer to document # 349-1057870, the Feature Function Definition for Controller Host Interface Card Management.

### 2.1.2.12. Push Button Support

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAWZCIC

In controllers prior to Pikes Peak, the serial port could be used to set the controller's management port IP addresses. This is useful if the IP address is unknown, and the controller is inaccessible via network. The Pikes Peak controller does not support traditional Serial Port Recovery Interface (SPRI) and instead contains a hardware push button. Pressing the pushbutton immediately resets the external Ethernet ports IP configuration to the "Quick Start" IP configuration. This allows the management application to communicate with the platform and perform further configuration. Refer to document # 44340-00, Hypervisor AAD - Virtualized hardware resources for detailed information.

In addition to IP address reset, push button when pressed continuously for 5 seconds, during reboot, allows controller to boot in a pre-defined order as follows:

1. Preboot eXecution Environment (PXE) - This option requires a Trivial File Transfer Protocol (TFTP) server running somewhere in the network with required boot image.

2. Boot from the installed SATA flash disks - This is the default mode and does not require push button to be pressed.

**Architecture Note:** Internal NIC IP address configuration is not affected by Push button.

**Architecture Note:** Boot order is still in an early stage and may change as we get more information. I have removed booting from USB option as we want to keep it as a hidden option.

**Architecture Note:** PXE boot is not committed for stage 1 yet.

### 2.1.2.13. USB Port

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAN3CIC

The USB port on controller is unsupported and a device plugged into USB port is not recognized.

**Architecture Note:** It is possible, though not desired, to PXE boot via USB if no tftp servers are found on the network. This port can also be used to boot the controller from LSI provided bootable USB drive, but this option is hidden and should be used by LSI designated support personnel. The USB port must be disabled by firmware in Domain0.

### 2.1.2.14. miniUSB Port

**Topic ID:** 2010-03-11T16:21:00Z-2258-12872-IDANZSMF

The Pikes Peak controller has one mini-USB style connector providing an external RS232 serial connection. The behavior of this port is same as serial port on platforms prior to Pikes Peak.

### 2.1.2.15. Power Supply

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAOADIC

The power supply on Pikes Peak controller supports PMBus protocol. Refer to document # 42253-00, the Feature Function Definition for SBB 2.0 VPD Data Support, for detailed information.

### 2.1.2.16. Wake on LAN Support (WOL)

**Topic ID:** 2009-11-02T15:32:00Z-2419-13791-IDAQBDIC

The Ethernet management ports on Pikes Peak controller support WOL.

**Architecture Note:** It is yet to be determined whether firmware needs to support WOL in first out.

## 2.2. Controller Type Mismatch - Element Requirements

### 2.2.1. Introduction

The Pikes Peak controller can be replaced with the same controller type. There are two versions of Pikes Peak controllers: a). PP200 and b). PP400. These two versions of controllers are treated as two different controller types and results in controller type mismatch if inter-mixed in same enclosure. In addition to this, host interface card on both the controllers must match for a supported configuration.

**Architecture Note:** Some of the information in the Element Requirement is from existing FFD, but most of the sections have some changes.

### 2.2.2. Operational Behavior

#### 2.2.2.1. Controller Hot-Swapped with Incorrect Controller Type

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDAUPP5B

Let's assume that controller A is inadvertently replaced with the incorrect controller type while controller B is operational. The outcome is as follows:

- Controller A continues to boot either from the functional partition in SATA flash on Pikes Peak or from on-board flash on platforms prior to Pikes Peak.

- Controller A enters the suspended state as a result of board ID mismatch.

- Upon insertion of controller A, the controller B detects the board ID mismatch and generates event notification as described in [Section 2.2.4.1. Controller Type Mismatch](#).

#### 2.2.2.2. Controller Hot-Swapped with same Controller Type

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDASSP5B

Let's assume that controller A is replaced with the same controller type while controller B is operational. The outcome is as follows:

- The controller A continues to boot from the functional partition in SATA flash.

- The controller A performs auto code synchronization if it is running different firmware than the firmware running on incumbent controller. Auto Code Synchronization rules are defined in Serviceability AAD - ACS and Controller Sparing element.

- The controller reboots once the firmware is re-flashed from the incumbent controller.

#### 2.2.2.3. Controller A or B Cold-Swapped with Incorrect Controller Type

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDA20P5B

This scenario occurs when one of the controllers is inadvertently replaced with the incorrect controller type when the enclosure is powered off. The outcome is as follows:

- When power is applied to the enclosure, both the controllers continue to boot either from the functional partition in SATA flash on Pikes Peak or from on-board flash on platforms prior to Pikes Peak.

- Both controllers enter the suspended state due to board ID mismatch.

- The storage array is not capable of performing host I/O operations until one of the controllers is removed.

#### 2.2.2.4. Power Cycle after Hot-Swap with Incorrect Controller Type

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDAV3P5B

If the enclosure is power-cycled with mismatched controller types after one of the controllers had previously been hot-swapped with incorrect controller type, the outcome is the same as if a controller had been cold-swapped with the incorrect controller type.

#### 2.2.2.5. Controller-Drive Enclosure Considerations

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDAA5P5B

Controller canister slots in controller-drive enclosures are designed to accept either a storage array controller, or an Environmental Services Monitor (ESM). ESMs are used in drive expansion enclosures that are attached to controller and controller-drive enclosures. If a controller is present in one slot and an ESM is present in the other slot, the controller will behave as if the ESM were a controller of a different type. This will result in controller type mismatch.

#### 2.2.2.6. Dual Controller Swap

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDAUUR5B

The dual controller swap behavior remains same as on previous platforms. Refer to existing FFD for more details.

**Architecture Note:** This behavior will change once NAS is introduced as cluster configuration needs to be handled. There might be few other things. The details should be handled in Serviceability AAD - ACS and controller sparing aspect element.

#### 2.2.2.7. Start-of-Day Mismatch Detection

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDAEVR5B

After each cold boot, the controller attempts to obtain the controller baseboard ID and host interface ID(s) from the alternate controller. If there is a mismatch in any pair of identifiers (base controller-alternate base controller, host card-alternate host card), the booting controller enters a suspended state and performs the following actions:

- The controller performs a self-lockdown and suspends normal operations.

- If the controller has a seven-segment display, a mismatched controller type lock-down code is displayed. The lock-down codes are defined in document # 34533-00, the Feature Function Definition for Controller Module Indicators.

- Management services (via SYMbol, CORBA etc.) are not available.

**Architecture Note:** Lockdown behavior is defined in serviceability AAD - Controller State Management.

### 2.2.2.8. Run-Time Mismatch Detection

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDAJYR5B

When a controller is hot inserted, the in-place controller attempts to obtain the controller board ID and host interface ID of the hot inserted controller. If there is a mismatch in any pair of identifiers, the in-place controller generates event notification as described in [Section 2.2.4.1. Controller Type Mismatch](#). The status for the newly inserted controller is set to be suspended.

### 2.2.2.9. Failure to Determine Alternate Board Identifier

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDA1ZR5B

If the alternate board identifiers cannot be determined, the in-place controller does not report the mismatched controller error. Instead, the controller reports:

- A Needs Attention condition.

- A critical MEL event indicating that the alternate board identifier could not be determined.

- A Recovery Guru procedure indicating that the alternate board identifier could not be determined.

- The replaced controller either enters the SBB validation failure state or controller type mismatch state if it is not able to validate the board identifier with the in-place controller. The SBB validation failure is described in document # 42253, the Feature Function Definition for SBB 2.0 VPD Data Support.

## 2.2.3. Administrative and Configuration Interfaces

### 2.2.3.1. Controller Mismatch Reporting

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDAD3R5B

**Architecture Note:** There is no change in existing reporting. Refer to existing FFD.

## 2.2.4. Error Handling and Event Notification

### 2.2.4.1. Controller Type Mismatch

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDA54R5B

As indicated in previous sections, a controller that detects a controller type mismatch during cold boot performs a self-lockdown and enters the suspended state. A controller that is suspended due to a type mismatch will automatically leave the suspended state and resumes normal operations if the alternate controller is removed.

**Architecture Note:** This is an existing behavior.

### 2.2.4.2. Device Reported Events

**Topic ID:** 2009-11-02T15:32:00Z-1780-10151-IDARQPAC

The Pikes Peak controller will continue to have existing MEL events and Recovery Guru.

## 2.3. Host Interface Cards - Element Requirements

### 2.3.1. Introduction

The Pikes Peak base controller has four Fibre Channel (FC) ports for host connectivity. Each port supports data rate of 2, 4, or 8 Gb/s and the connectivity to the host ports is provided through SFP+ interfaces. In addition to the FC ports on base controller, Pikes Peak controller also has a provision to support InfiniBand (IB), iSCSI, or additional FC ports through an optional Host Interface Card (HIC). The HIC form factor for Pikes Peak controller is not compatible with HICs developed for platforms prior to Pikes Peak.

### 2.3.2. Operational Behavior

Following sub-sections describe the behavior for different HICs on Pikes Peak controller.

#### 2.3.2.1. Fibre Channel Host Interface Card (Manitou)

**Topic ID:** 2009-11-02T15:15:00Z-516-2943-IDAUPBRC

Pikes Peak controller has a provision to attach an additional FC HIC, Manitou. The Manitou card supports four FC ports where each port supports data rate of 2, 4 or 8 Gb/s. With this HIC, there are a total of 8 FC ports available on Pikes Peak. The FC ports only support FCP upper-layer protocol. Only direct and FC fabric connections are supported; FC-AL attached to an FC fabric is not supported.

The LED behavior for the HIC is same as described in document # 34533-00, the Feature Function Definition for Controller Module Indicators.

#### 2.3.2.2. InfiniBand Host Interface Card (Elk Park)

**Topic ID:** 2009-11-02T15:15:00Z-516-2943-IDA4QBRC

Pikes Peak controller also has a provision to attach an InfiniBand HIC, Elk Park. The Elk Park card supports two IB ports where each port supports data rate up to 40 Gb/s. The IB host card interconnects via an InfiniBand switch fabric. The LED behavior for the HIC is same as described in document # 34533-00, the Feature Function Definition for Controller Module Indicators.

Refer to Feature Function Definition document # 349-1061360 for more information about InfiniBand host port functionality.

**Architecture Note:** Document # 34533-00, the Feature Function Definition for Controller Module Indicators needs to be updated for IB LED indicators.

#### 2.3.2.3. iSCSI-SFP+ Host Interface Card (Glen Cove)

**Topic ID:** 2009-11-02T15:15:00Z-516-2943-IDASSBRC

Pikes Peak controller also has a provision to attach an Ethernet/iSCSI HIC, Glen Cove. The Glen Cove card supports two Ethernet ports where each port supports data rate of 10 Gb/s. Each Ethernet port is implemented by separate PCI functions for unaccelerated Ethernet protocol and accelerated iSCSI Initiator/Target protocol. The iSCSI Initiator and iSCSI Target functions may optionally be implemented by separate PCI functions.

The LED behavior for the HIC is same as described in document # 34533-00, the Feature Function Definition for Controller Module Indicators.

## 2.4. SATA Flash Disk Support - Element Requirements

### 2.4.1. Introduction

The SATA Flash disk is a new component on Pikes Peak. It has several partitions: storage for functional code, storage for logs, storage for configurations, storage for core files, and storage for cache offload.

The PP200 and PP400 have two SATA flash disks of capacity 8 GB for a total of 16 GB.

**Architecture Note:** if a single PP type supports more than 1 flash configuration, then it affects functionality associated with upgrade from block only to block + file. in essence, we are trying to ensure that when a user moves from b-o to b+f, we also do not have to worry about flash drive replacements.

### 2.4.2. Operational Behavior

#### 2.4.2.1. Partitioning

**Topic ID:** 2009-11-02T15:15:00Z-1064-6067-IDALQBRC

Pikes Peak uses Master Boot Record (MBR) partitioning scheme. This is the traditional layout used in PC operating systems. Broadly, Partitions can be categorized into two categories: Raw partitions and the partitions with the file systems

Raw partitions:

- Partition for IOVM Cache Offload